Part Number: TMS320F280039C

Hello,

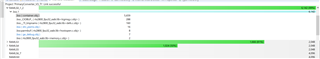

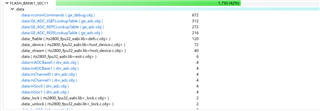

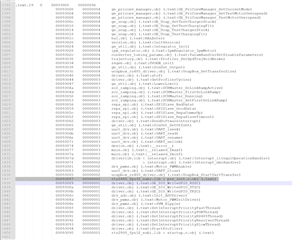

I have several questions about the bootloader example "flash_kernel_ex3_sci_flash_kernel". I have been using this as a reference for creating a bootloader for my own application. I was able to understand erasing, programming and verifying sections of the flash. However, when jumping to the user application this is where I am confused.

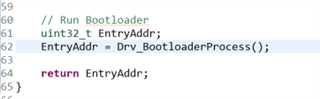

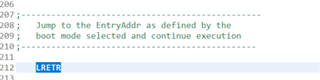

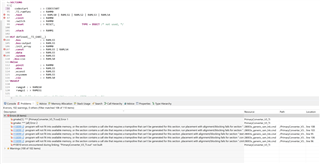

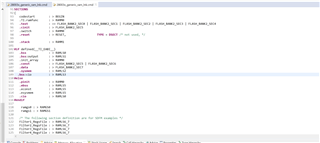

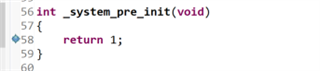

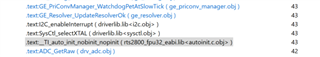

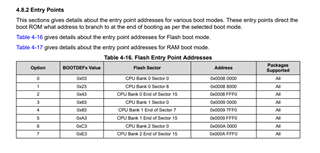

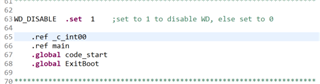

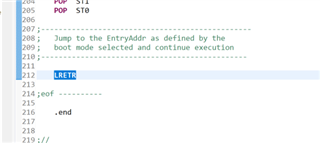

It looks like "flash_kernel_ex3_codestartbranch" causes a watchdog failure to reset the MCU and then boots up at location _c_int00.

Questions -

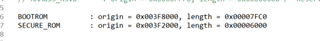

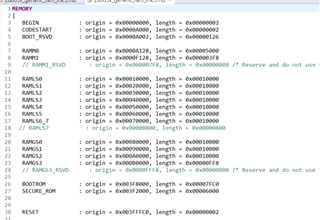

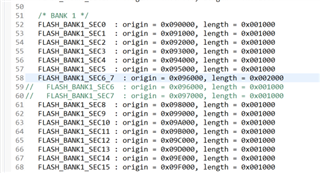

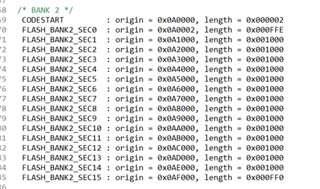

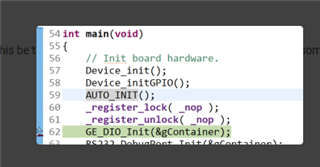

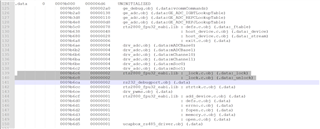

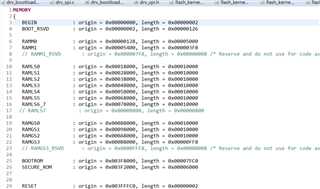

1 - Where is _c_int00 defined? I want my user application to match another microcontroller also used in my application. I'm trying not to change my master controller code that interfaces with this microcontoller and I want to only change the microcontroller code. I want my user application to be defined to start at 0xA000. How do I define flash_kernel_ex3_codestartbranch.asm to jump there?

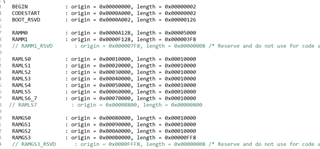

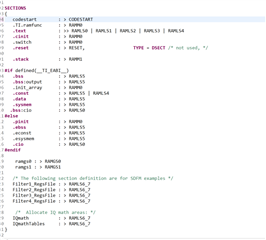

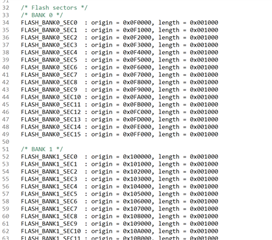

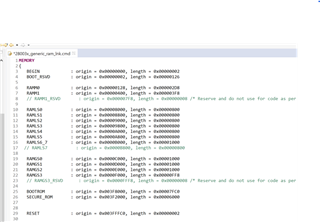

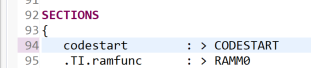

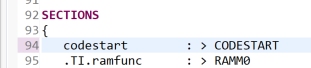

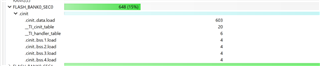

2 - In my user application, how would I define the code to start at 0xA000? Do I change BEGIN below to 0xA000?

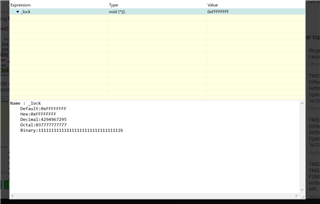

3 - In "flash_kernel_ex3_codestartbranch.asm" what is the EntryAddr and how would I define it in such a way to jump to 0xA000 if the programming succeeded and 0x0000 (where I want the bootloader to live) if the programming failed? I see EntryAddr in the code and I assume it's being defined from the data read on SCI but I cannot see what the data coming over SCI is. I want to just set EntryAddr to either jump to restart bootloader at 0x0000 or jump to user application at 0xA000.

Thanks for the help!