Part Number: TMS320F28379D

Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Tool/software:

Hello,

It's me, again.

I closed this issue, because the explanation was very clear (many thanks)

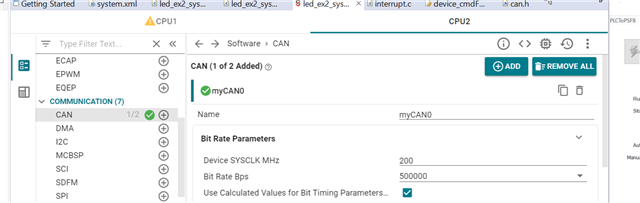

So, I started to include that into my project, but it did not work. Why ? My project includes CAN functionality. So, I join the same example as resolved, but with CAN addition.

And let me explain down below what happens:

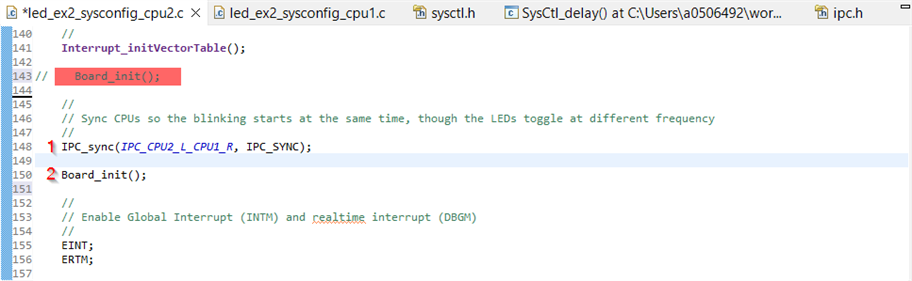

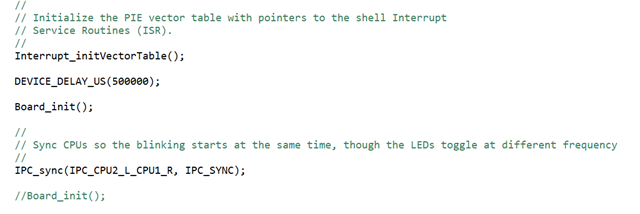

1) The project is the same as before, but I added a CAN peripheral in the SysConfig. I will not use it. I just want the project to initialize this peripheral in board.c:

2) I launch a debug session with FLASH configuration. So, when the CPU2 will reset, it will not erase the code in RAM, which is usefull for the code start

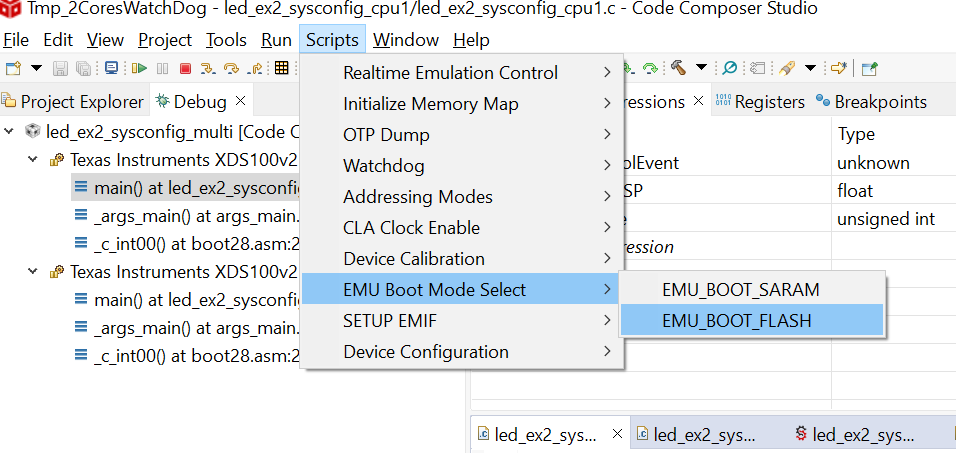

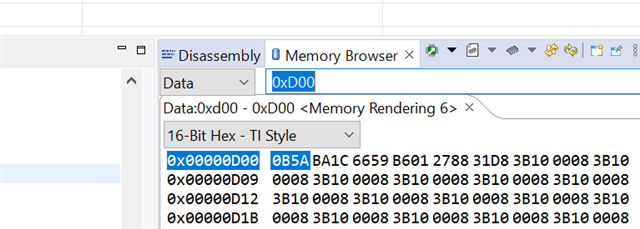

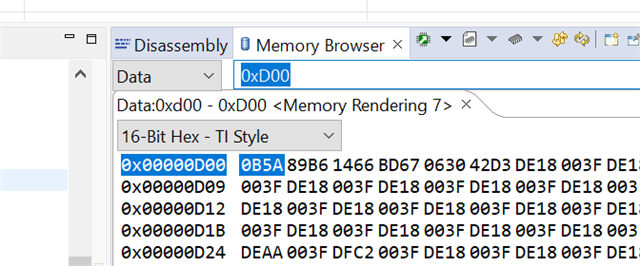

3) Before to run each core, I launch the script EMU_BOOT_FLASH and check that 0xOB5A is written at the adresses 0xD00:

(CPU1)

(CPU2)

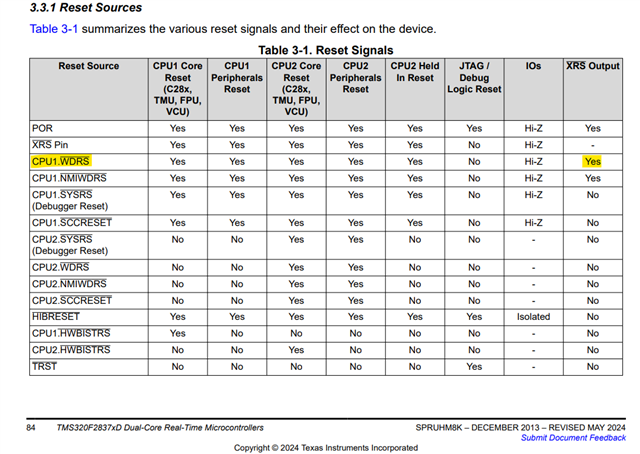

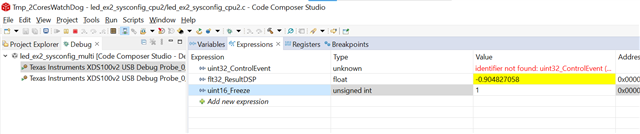

3) When setting the variable uint16_Freeze, the CPU1 enters into a infinite while loop, and the ISR of the Watchdog asks for a reset of the CPU1 and CPU2:

4) I cannot see any error message in the debug session, but I clearly see that the programm does not run anymore

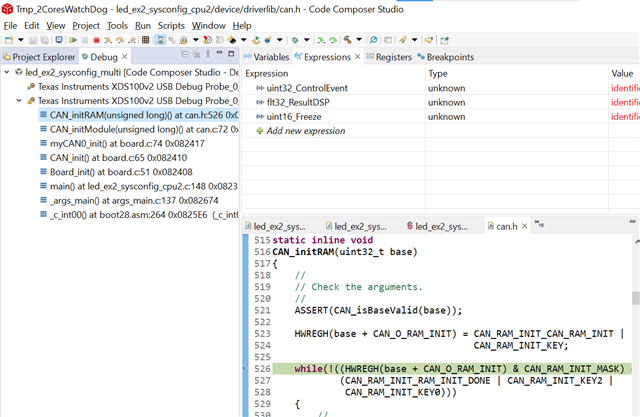

If I set the CPU2 on pause, I can see that the programm is blocked in the CAN RAM init function:

I suppose that the problem is linked to the RAM erasing.

Can somebody tell me exactly what is wrong ? Will it happen in the standalone configuration ? How can I do to test the watchdog fonctionnality in a debug session ?

Thank you.