Other Parts Discussed in Thread: UNIFLASH, LAUNCHXL-F28379D, C2000WARE, SYSCONFIG

Tool/software:

Hi Team,

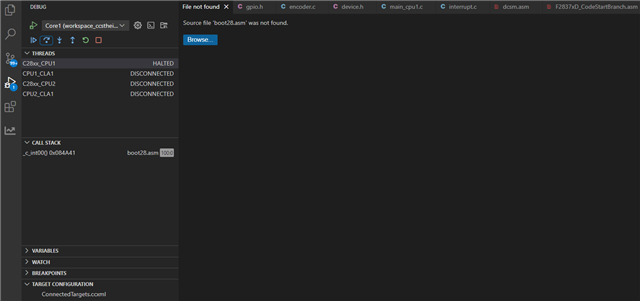

We are experiencing an issue where we observe that the code not executing after cutting off the power to the MCU and then giving it back again after sometime.

We have designed a custom board for our motor control application using TMS320F28379D. Currently we are powering it through the launchpad (LAUNCHXL f28379D) since our another board (Power board) which we have designed to power this custom board has not arrived yet.

The code(firmware) that we have flashed is a simple LED blinking on our custom board.

So, we are investigating what could be the issue for this behaviour?

Could it be an Hardware issue or could it be a firmware issue ?

We would appreciate your help to identify the cause. Do let me know if you have any suggestions for us to check and verify in this design.