Part Number: C2000WARE

Other Parts Discussed in Thread: TMS320F280049C, TMS320F280049-Q1

Tool/software:

Hello Support,

We have developed an airborne application based on the 280049 microcontroler whose drivers are mainly derived from C2000ware version 4.3 for CLOCK/PLL setting and control (sysctl.c)

Today, while reviewing our code and comparing it to the latest version of C2000ware (5.05) and the latest release of TRM, we noticed that certain timings and retries have been modified

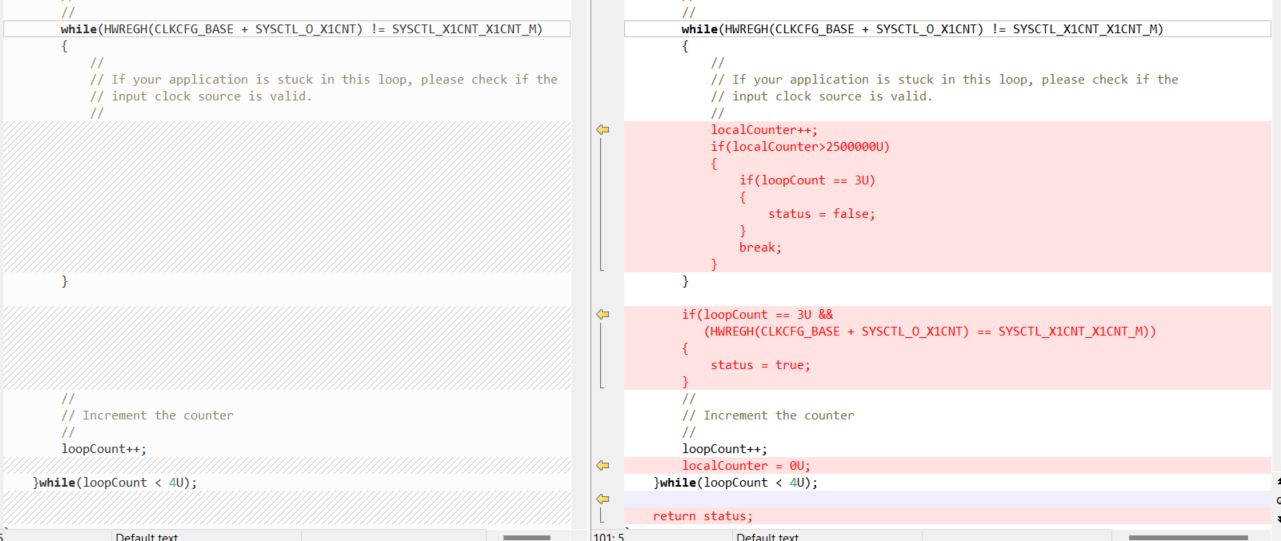

1) when waiting for X1 clock to saturate

added a timeout option to exit the loop :

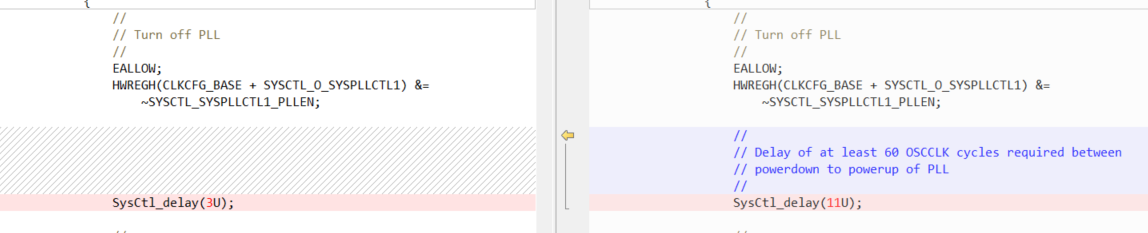

2) when turning off the PLL

added a Delay of at least 60 OSCCLK cycles required between powerdown to powerup of PLL

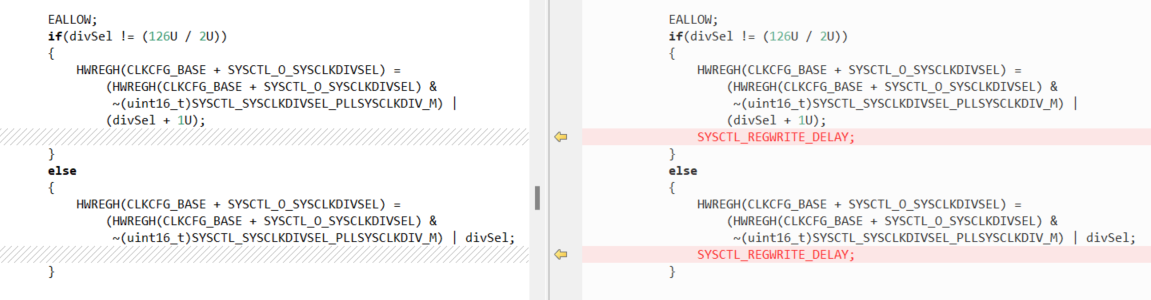

3) when writing the divider in SYSCTL_O_SYSCLKDIVSEL / SYSCTL_O_XTALCR / SYSCTL_O_CLKSRCCTL1 registers

added a delay

SYSCTL_REGWRITE_DELAY i.e. asm(" RPT #39 || NOP")

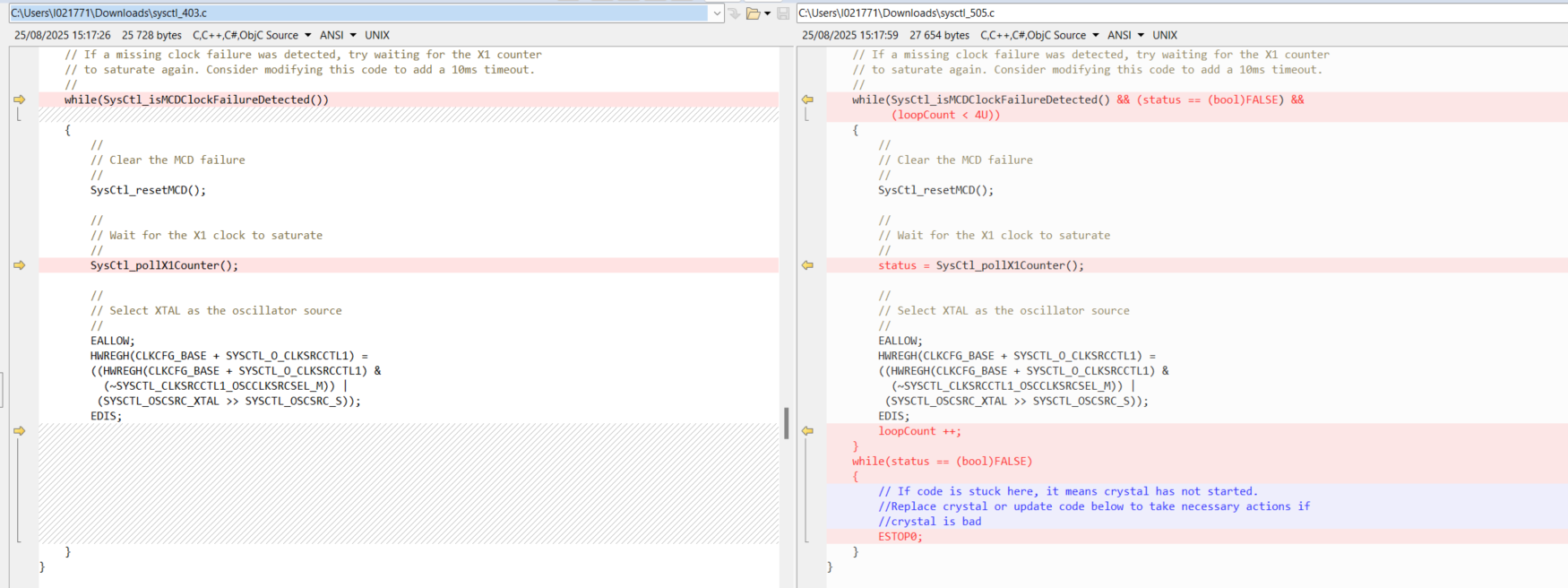

4) When checking missing clock failure

added a counter option to exit the loop , and stop the program execution

Can we live without these changes or they really must be implemented in our code ?

We are at a stage where modifying our code will require us to rerun all our high-level tests and replay some low level tests.

Thank you by advance.

David