Part Number: TMS320F280025

Tool/software:

Hello,

I’m working on a project with the TMS320F280025 microcontroller, C2000 v5.0.00.00, and the Safety Diagnostic Library v4.01.00.

The system is based on two interrupts:

- Timer2 (with 500ms period): Inside the ISR, the CPUTIMER_TCR_TIF is cleared as required in the thread:

TMS320F280025: Spurious interrupts after HWBIST test - ADC (with 55µs period): On every occurrence of the ISR, an STL_HWBIST_runMicro is executed until the HWBIST test is completed. After that, the FLASH ECC test is executed for a certain number of cycles in order to run correctable and uncorrectable tests… Then the cycle restarts from the HWBIST test.

- There are no other interrupts interfering with normal operation, and the system schedules correctly.

I have noticed that sometimes the execution of timer2_ISR is delayed by a time equal to the number of ADC_ISR cycles during which the flash tests are executed. After that, it seems that the execution of STL_HWBIST_runMicro restores normal operation.

The problem does not seem to occur in two different cases, namely when:

- CPUTIMER_TCR_TIF is not cleared by timer2_ISR (and therefore without the HWBIST test, since that would imply spurious timer2 interrupts).

- The instructions related to IER, PIEIER12, and EINT/DINT are not executed inside the else statement of the ADC_ISR.

Thank you in advance for your support.

Here the code:

__interrupt void timer2_ISR(void)

{

// Some code...

// Clear the overflow flag — this is mandatory to avoid spurious interrupts

// after HWBIST micro-run execution.

CPUTimer_clearOverflowFlag(CPUTIMER2_BASE);

}

interrupt void ADC_ISR(void)

{

// Some code...

// Acknowledge interrupt group 1 to allow further interrupts from this group

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP1);

if (condition == 1)

{

// Some code...

// Execute HWBIST micro-run

STL_HWBIST_runMicro();

// Some code...

}

else

{

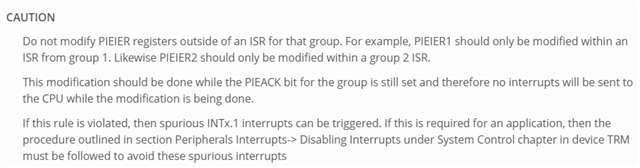

uint16_t pieier_prev = HWREGH(PIECTRL_BASE + PIE_O_IER12);

// IER: disable all interrupt except for the group 12 and ERAD.

IER &= INTERRUPT_CPU_INT12 | INTERRUPT_CPU_RTOSINT;

// PIEIER12: disable all interrupt of group 12

// except the flash correctable error interrupt.

HWREGH(PIECTRL_BASE + PIE_O_IER12) &= PIE_IER12_INTX11;

// Enable interrupts.

EINT;

// Perform a flash selftest.

flash_selftest();

// Disable interrupts.

DINT;

// Restore interrupts registers.

HWREGH(PIECTRL_BASE + PIE_O_IER12) = pieier_prev;

}

}