Hi Trey,

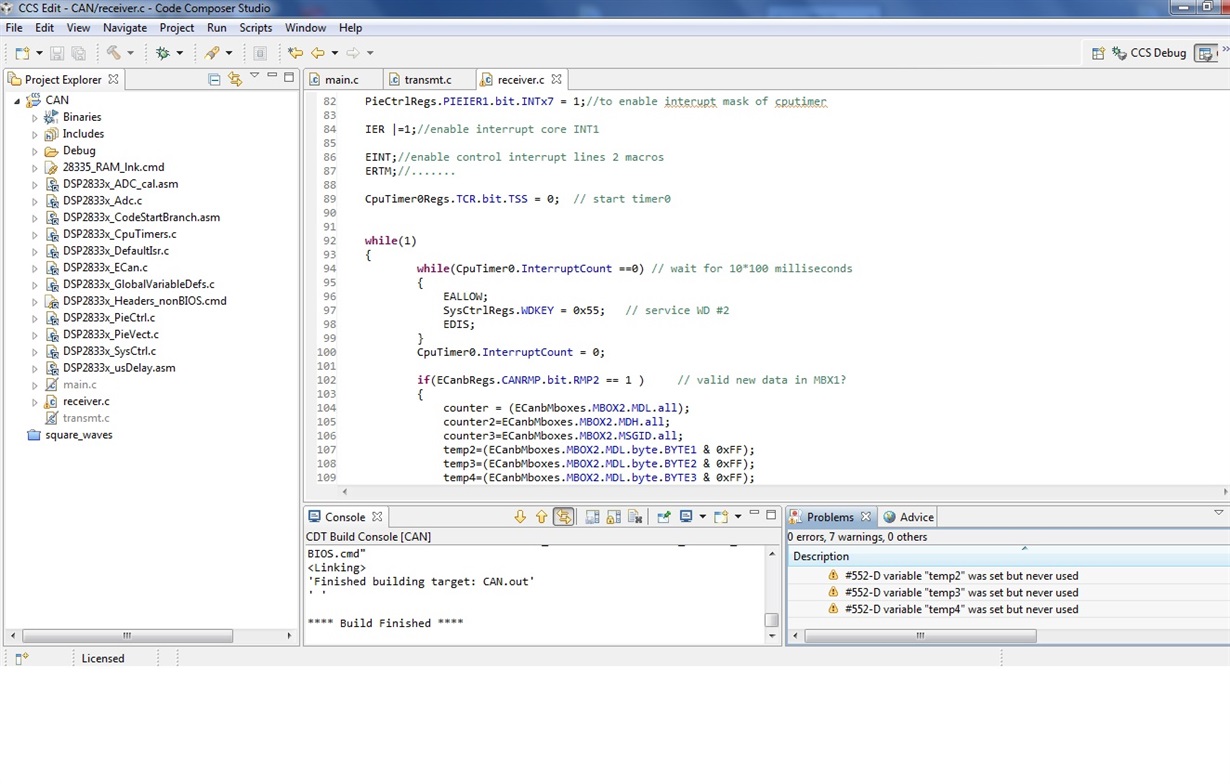

I have faced a trouble with CAN communication.I'm workin on Delfino experimenter kit has F28335 controlCard.

//

// Lab5_1: TMS320F28335

// (c) Frank Bormann

//

//###########################################################################

//

//

// FILE: Lab11_2.c

//

// TITLE: CAN - Receive via F28335controlCARD

// and SH65HVD230 at Peripheral Explorer Board

//

// Extended CAN-Frame is received with 100 kbit/s

//

// Objective:

// Receive a 1 Byte data frame with Identifier 0x10000000

// and display 4 least significant bits of byte0 at 4 LEDs

//

// Mailbox 1 is receiver

// Identifier : 0x1000 0000

// Data Length Code (DLC) = 1

// eCANA is at GPIO31 (CANTXA) and GPIO30 (CANRXA)

//

// Frequency Osscillator @F28335controlCARD: 30MHz

// PLLCR = 10 : multiply by 5

// SYSCLKOUT = 150MHz , 28335-CAN-CLKIN = 75MHz

// CAN - Bit timing set in file "DSP2833x_ECan.c" for 100 kbit/s:

// TQ = (49 +1) / 75 MHz = 0.667 us: BRPREG = 49

// tseg1 = 1us (10+1) = 7.333 us; TSEG1REG = 10

// tseg2 = 1us (2+1) = 2 us; TSEG2REG = 2

// By A.A

//Editing: Used F28335 controlCARD Release 2.2,TMDSCNCD28335 R2.2

// Extended Can frame is received with 208.33 kbit/s

// objective:

// Receive 4 byte data frame with identifier 0x000007D5 // unsigned long ID= 2005

// eCANA is at GPIO31 (CANTXA) and GPIO30 (CANRXA)

// Frequency Osscillator @F28335controlCARD: 30MHz

// PLLCR = 10 : multiply by 5

// SYSCLKOUT = 150MHz , 28335-CAN-CLKIN = 75MHz

// CAN - Bit timing set in file "DSP2833x_ECan.c" for 208.33 kbit/s:

// TQ = (23 +1) / 75 MHz = 0.32 us: BRPREG = 23

// tseg1 = 0.32u*(10+1) = 3.52 us; TSEG1REG = 10

// tseg2 = 0.32u* (2+1) = 0.96 us; TSEG2REG = 2

// tcan=tseg1+tseg2+TQ=3.52+0.96+0.32=4,8u => 208,3333333kbit/s

//

// GPIO pins are used to display the received data on 16 leds

// This written code for listener node whose talker node sends 4 byte data every 10ms

//

//###########################################################################

// Ver | dd mmm yyyy | Who | Description of changes

// =====|=============|======|===============================================

// 3.0 | 02 May 2008 | F.B. | Lab5_1 for F28335;

// 3.1 | 06 Nov 2009 | F.B | Lab5_1 for F28335 and PE revision5

//###########################################################################

#include "DSP2833x_Device.h"

// external function prototypes

extern void InitSysCtrl(void);

extern void InitPieCtrl(void);

extern void InitPieVectTable(void);

extern void InitCpuTimers(void);

extern void InitECan(void);

extern void ConfigCpuTimer(struct CPUTIMER_VARS *, float, float);

extern void InitECan(void);

// Prototype statements for functions found within this file.

void Gpio_select(void);//I/O se�imi,register ayarlar1

interrupt void cpu_timer0_isr(void);

//###########################################################################

// main code

//###########################################################################

void main(void)

{

struct ECAN_REGS ECanaShadow; // local copy of CANA registers

Uint16 temp;//1st byte

Uint16 temp2;//2nd byte

Uint16 temp3;//3th byte

Uint16 temp4;//4th byte

InitSysCtrl(); // Basic Core Init from DSP2833x_SysCtrl.c

EALLOW;

SysCtrlRegs.WDCR= 0x00AF; // Re-enable the watchdog

EDIS; // 0x00AF to NOT disable the Watchdog, Prescaler = 64

DINT; // Disable all interrupts

Gpio_select();

/* Initialize the CAN module */

// NOTE: first modify TI-file: InitECan() to 100kbps by setting BTR = 49

//edit:changed the values to 208.33kbps by setting BTR=23

InitECan();

/* Write to Mailbox 1 message ID field */

ECanaMboxes.MBOX1.MSGID.all = 0x000007D5; // messsage ID=2005 is set as integer

ECanaMboxes.MBOX1.MSGID.bit.IDE = 1; // Extended Identifier

/* Configure Mailbox 1 as Receiver mailbox */

ECanaShadow.CANMD.all = ECanaRegs.CANMD.all;

ECanaShadow.CANMD.bit.MD1 = 1;

ECanaRegs.CANMD.all = ECanaShadow.CANMD.all;

/* Enable Mailbox 1 */

ECanaShadow.CANME.all = ECanaRegs.CANME.all;

ECanaShadow.CANME.bit.ME1 = 1;

ECanaRegs.CANME.all = ECanaShadow.CANME.all;

InitPieCtrl(); // clear all pending PIE-Interrupts and to disable all PIE interrupt lines

InitPieVectTable(); // default ISR's in PIE,This function will initialize the PIE-memory to an initial state.

EALLOW;//Cputimeri PIE icerisinden re-map ediyoruz

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS;

InitCpuTimers(); // basic setup CPU Timer0, 1 and 2,Timer0 set edildi

ConfigCpuTimer(&CpuTimer0,150,100000); // CPU - Timer0 at 100 milliseconds

//parametre1=adress of core,parametre2=internal speed of DSP,paramtre3=period time for timer overflow

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;//to enable interupt mask of cputimer

IER |=1;//enable interrupt core INT1

EINT;//enable control interrupt lines 2 macros

ERTM;//.......

CpuTimer0Regs.TCR.bit.TSS = 0; // start timer0

while(1)

{

while(CpuTimer0.InterruptCount == 0);

CpuTimer0.InterruptCount = 0;

EALLOW;

SysCtrlRegs.WDKEY = 0x55; // service WD #1

EDIS;

if(ECanaRegs.CANRMP.bit.RMP1== 1 ) // control valid new data in MBX1?

{

temp = ECanaMboxes.MBOX1.MDL.byte.BYTE0; // byte zero read message,load it temp,

temp2=ECanaMboxes.MBOX1.MDL.byte.BYTE1;

temp3=ECanaMboxes.MBOX1.MDL.byte.BYTE2;

temp4=ECanaMboxes.MBOX1.MDL.byte.BYTE3;

ECanaRegs.CANRMP.bit.RMP1 = 1; // clear the status flag RMP1

if(temp&1) GpioDataRegs.GPBSET.bit.GPIO59=1;

else GpioDataRegs.GPBCLEAR.bit.GPIO59 = 1;

if(temp&2) GpioDataRegs.GPBSET.bit.GPIO61=1;

else GpioDataRegs.GPBCLEAR.bit.GPIO61=1;

if(temp&4) GpioDataRegs.GPASET.bit.GPIO1=1;

else GpioDataRegs.GPACLEAR.bit.GPIO1=1;

if(temp&8) GpioDataRegs.GPASET.bit.GPIO3=1;

else GpioDataRegs.GPACLEAR.bit.GPIO3=1;

if(temp2&1) GpioDataRegs.GPASET.bit.GPIO5=1;

else GpioDataRegs.GPACLEAR.bit.GPIO5=1;

if(temp2&2) GpioDataRegs.GPASET.bit.GPIO7=1;

else GpioDataRegs.GPACLEAR.bit.GPIO7=1;

if(temp2&4) GpioDataRegs.GPASET.bit.GPIO9=1;

else GpioDataRegs.GPACLEAR.bit.GPIO9=1;

if(temp2&8) GpioDataRegs.GPASET.bit.GPIO11=1;

else GpioDataRegs.GPACLEAR.bit.GPIO11=1;

if(temp3&1) GpioDataRegs.GPBSET.bit.GPIO49=1;

else GpioDataRegs.GPBCLEAR.bit.GPIO49=1;

if(temp3&2) GpioDataRegs.GPCSET.bit.GPIO85=1;

else GpioDataRegs.GPCCLEAR.bit.GPIO85=1;

if(temp3&4) GpioDataRegs.GPASET.bit.GPIO13=1;

else GpioDataRegs.GPACLEAR.bit.GPIO13=1;

if(temp3&8) GpioDataRegs.GPASET.bit.GPIO14=1;

else GpioDataRegs.GPACLEAR.bit.GPIO14=1;

if(temp4&1) GpioDataRegs.GPASET.bit.GPIO25=1;

else GpioDataRegs.GPACLEAR.bit.GPIO25=1;

if(temp4&2) GpioDataRegs.GPASET.bit.GPIO21=1;

else GpioDataRegs.GPACLEAR.bit.GPIO21=1;

if(temp4&4) GpioDataRegs.GPASET.bit.GPIO23=1;

else GpioDataRegs.GPACLEAR.bit.GPIO23=1;

if(temp4&8) GpioDataRegs.GPASET.bit.GPIO29=1;

else GpioDataRegs.GPACLEAR.bit.GPIO29=1;

}

}

}

void Gpio_select(void)

{

EALLOW;

GpioCtrlRegs.GPAMUX1.all = 0; // GPIO15 ... GPIO0 = General Puropse I/O

GpioCtrlRegs.GPAMUX2.all = 0; // GPIO31 ... GPIO16 = General Purpose I/O

GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 1; // CANA_RX

GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 1; // CANA_TX

GpioCtrlRegs.GPBMUX1.all = 0; // GPIO47 ... GPIO32 = General Purpose I/O

GpioCtrlRegs.GPBMUX2.all = 0; // GPIO63 ... GPIO48 = General Purpose I/O

GpioCtrlRegs.GPCMUX1.all = 0; // GPIO79 ... GPIO64 = General Purpose I/O

GpioCtrlRegs.GPCMUX2.all = 0; // GPIO87 ... GPIO80 = General Purpose I/O

GpioCtrlRegs.GPADIR.all = 0;

GpioCtrlRegs.GPADIR.bit.GPIO1=1;

GpioCtrlRegs.GPADIR.bit.GPIO3=1;

GpioCtrlRegs.GPADIR.bit.GPIO5=1;

GpioCtrlRegs.GPADIR.bit.GPIO7=1;

GpioCtrlRegs.GPADIR.bit.GPIO9=1;

GpioCtrlRegs.GPADIR.bit.GPIO11=1;

GpioCtrlRegs.GPADIR.bit.GPIO13=1;

GpioCtrlRegs.GPADIR.bit.GPIO14=1;

GpioCtrlRegs.GPADIR.bit.GPIO25=1;

GpioCtrlRegs.GPADIR.bit.GPIO27=1;

GpioCtrlRegs.GPADIR.bit.GPIO21=1;

GpioCtrlRegs.GPADIR.bit.GPIO23=1;

GpioCtrlRegs.GPADIR.bit.GPIO29=1;

GpioCtrlRegs.GPBDIR.all = 0; // GPIO63-32 as inputs

GpioCtrlRegs.GPBDIR.bit.GPIO49=1;

GpioCtrlRegs.GPBDIR.bit.GPIO59=1;

GpioCtrlRegs.GPBDIR.bit.GPIO61=1;

GpioCtrlRegs.GPCDIR.all=0;//lines in c will be digital input

GpioCtrlRegs.GPCDIR.bit.GPIO85=1;

EDIS;

}

interrupt void cpu_timer0_isr(void)

{

CpuTimer0.InterruptCount++;

EALLOW;

SysCtrlRegs.WDKEY = 0xAA; // service WD #2

EDIS;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}

//===========================================================================

// End of SourceCode.

//===========================================================================

// TI File $Revision: /main/8 $

// Checkin $Date: June 25, 2008 15:19:07 $

//###########################################################################

//

// FILE: DSP2833x_ECan.c

//

// TITLE: DSP2833x Enhanced CAN Initialization & Support Functions.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

#include "DSP2833x_Device.h" // DSP2833x Headerfile Include File

#include "DSP2833x_Examples.h" // DSP2833x Examples Include File

//---------------------------------------------------------------------------

// InitECan:

//---------------------------------------------------------------------------

// This function initializes the eCAN module to a known state.

//

void InitECan(void)

{

InitECana();

#if DSP28_ECANB

InitECanb();

#endif // if DSP28_ECANB

}

void InitECana(void) // Initialize eCAN-A module

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents or return

false data. This is especially true while writing to/reading from a bit

(or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanaShadow;

EALLOW; // EALLOW enables access to protected bits

/* Configure eCAN RX and TX pins for CAN operation using eCAN regs*/

ECanaShadow.CANTIOC.all = ECanaRegs.CANTIOC.all;

ECanaShadow.CANTIOC.bit.TXFUNC = 1;

ECanaRegs.CANTIOC.all = ECanaShadow.CANTIOC.all;

ECanaShadow.CANRIOC.all = ECanaRegs.CANRIOC.all;

ECanaShadow.CANRIOC.bit.RXFUNC = 1;

ECanaRegs.CANRIOC.all = ECanaShadow.CANRIOC.all;

/* Configure eCAN for HECC mode - (reqd to access mailboxes 16 thru 31) */

// HECC mode also enables time-stamping feature

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.SCB = 1;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

/* Initialize all bits of 'Master Control Field' to zero */

// Some bits of MSGCTRL register come up in an unknown state. For proper operation,

// all bits (including reserved bits) of MSGCTRL must be initialized to zero

ECanaMboxes.MBOX0.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX1.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX2.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX3.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX4.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX5.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX6.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX7.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX8.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX9.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX10.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX11.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX12.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX13.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX14.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX15.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX16.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX17.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX18.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX19.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX20.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX21.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX22.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX23.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX24.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX25.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX26.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX27.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX28.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX29.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX30.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX31.MSGCTRL.all = 0x00000000;

// TAn, RMPn, GIFn bits are all zero upon reset and are cleared again

// as a matter of precaution.

ECanaRegs.CANTA.all = 0xFFFFFFFF; /* Clear all TAn bits */

ECanaRegs.CANRMP.all = 0xFFFFFFFF; /* Clear all RMPn bits */

ECanaRegs.CANGIF0.all = 0xFFFFFFFF; /* Clear all interrupt flag bits */

ECanaRegs.CANGIF1.all = 0xFFFFFFFF;

/* Configure bit timing parameters for eCANA*/

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 1 ; // Set CCR = 1

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 1 ); // Wait for CCE bit to be set..

ECanaShadow.CANBTC.all = 0;

#if (CPU_FRQ_150MHZ) // CPU_FRQ_150MHz is defined in DSP2833x_Examples.h

/* The following block for all 150 MHz SYSCLKOUT (75 MHz CAN clock) - default. Bit rate = 208.33 khz bps

See Note at End of File */

//208.33kbit e g�re ayarland�

ECanaShadow.CANBTC.bit.BRPREG = 23;

ECanaShadow.CANBTC.bit.TSEG2REG = 2;

ECanaShadow.CANBTC.bit.TSEG1REG = 10;

#endif

#if (CPU_FRQ_100MHZ) // CPU_FRQ_100MHz is defined in DSP2833x_Examples.h

/* The following block is only for 100 MHz SYSCLKOUT (50 MHz CAN clock). Bit rate = 1 Mbps

See Note at End of File */

ECanaShadow.CANBTC.bit.BRPREG = 4;

ECanaShadow.CANBTC.bit.TSEG2REG = 1;

ECanaShadow.CANBTC.bit.TSEG1REG = 6;

#endif

ECanaShadow.CANBTC.bit.SAM = 1;

ECanaRegs.CANBTC.all = ECanaShadow.CANBTC.all;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 0 ; // Set CCR = 0

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 0 ); // Wait for CCE bit to be cleared..

/* Disable all Mailboxes */

ECanaRegs.CANME.all = 0; // Required before writing the MSGIDs

EDIS;

}

#if (DSP28_ECANB)

void InitECanb(void) // Initialize eCAN-B module

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents or return

false data. This is especially true while writing to/reading from a bit

(or group of bits) among bits 16 - 31 */

struct ECAN_REGS ECanbShadow;

EALLOW; // EALLOW enables access to protected bits

/* Configure eCAN RX and TX pins for CAN operation using eCAN regs*/

ECanbShadow.CANTIOC.all = ECanbRegs.CANTIOC.all;

ECanbShadow.CANTIOC.bit.TXFUNC = 1;

ECanbRegs.CANTIOC.all = ECanbShadow.CANTIOC.all;

ECanbShadow.CANRIOC.all = ECanbRegs.CANRIOC.all;

ECanbShadow.CANRIOC.bit.RXFUNC = 1;

ECanbRegs.CANRIOC.all = ECanbShadow.CANRIOC.all;

/* Configure eCAN for HECC mode - (reqd to access mailboxes 16 thru 31) */

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.SCB = 1;

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

/* Initialize all bits of 'Master Control Field' to zero */

// Some bits of MSGCTRL register come up in an unknown state. For proper operation,

// all bits (including reserved bits) of MSGCTRL must be initialized to zero

ECanbMboxes.MBOX0.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX1.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX2.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX3.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX4.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX5.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX6.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX7.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX8.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX9.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX10.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX11.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX12.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX13.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX14.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX15.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX16.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX17.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX18.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX19.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX20.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX21.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX22.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX23.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX24.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX25.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX26.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX27.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX28.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX29.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX30.MSGCTRL.all = 0x00000000;

ECanbMboxes.MBOX31.MSGCTRL.all = 0x00000000;

// TAn, RMPn, GIFn bits are all zero upon reset and are cleared again

// as a matter of precaution.

ECanbRegs.CANTA.all = 0xFFFFFFFF; /* Clear all TAn bits */

ECanbRegs.CANRMP.all = 0xFFFFFFFF; /* Clear all RMPn bits */

ECanbRegs.CANGIF0.all = 0xFFFFFFFF; /* Clear all interrupt flag bits */

ECanbRegs.CANGIF1.all = 0xFFFFFFFF;

/* Configure bit timing parameters for eCANB*/

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.CCR = 1 ; // Set CCR = 1

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

do

{

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

} while(ECanbShadow.CANES.bit.CCE != 1 ); // Wait for CCE bit to be cleared..

ECanbShadow.CANBTC.all = 0;

#if (CPU_FRQ_150MHZ) // CPU_FRQ_150MHz is defined in DSP2833x_Examples.h

/* The following block for all 150 MHz SYSCLKOUT (75 MHz CAN clock) - default. Bit rate = 1 Mbps

See Note at end of file */

ECanbShadow.CANBTC.bit.BRPREG = 4;

ECanbShadow.CANBTC.bit.TSEG2REG = 2;

ECanbShadow.CANBTC.bit.TSEG1REG = 10;

#endif

#if (CPU_FRQ_100MHZ) // CPU_FRQ_100MHz is defined in DSP2833x_Examples.h

/* The following block is only for 100 MHz SYSCLKOUT (50 MHz CAN clock). Bit rate = 1 Mbps

See Note at end of file */

ECanbShadow.CANBTC.bit.BRPREG = 4;

ECanbShadow.CANBTC.bit.TSEG2REG = 1;

ECanbShadow.CANBTC.bit.TSEG1REG = 6;

#endif

ECanbShadow.CANBTC.bit.SAM = 1;

ECanbRegs.CANBTC.all = ECanbShadow.CANBTC.all;

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.CCR = 0 ; // Set CCR = 0

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

do

{

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

} while(ECanbShadow.CANES.bit.CCE != 0 ); // Wait for CCE bit to be cleared..

/* Disable all Mailboxes */

ECanbRegs.CANME.all = 0; // Required before writing the MSGIDs

EDIS;

}

#endif // if DSP28_ECANB

//---------------------------------------------------------------------------

// Example: InitECanGpio:

//---------------------------------------------------------------------------

// This function initializes GPIO pins to function as eCAN pins

//

// Each GPIO pin can be configured as a GPIO pin or up to 3 different

// peripheral functional pins. By default all pins come up as GPIO

// inputs after reset.

//

// Caution:

// Only one GPIO pin should be enabled for CANTXA/B operation.

// Only one GPIO pin shoudl be enabled for CANRXA/B operation.

// Comment out other unwanted lines.

void InitECanGpio(void)

{

InitECanaGpio();

#if (DSP28_ECANB)

InitECanbGpio();

#endif // if DSP28_ECANB

}

void InitECanaGpio(void)

{

EALLOW;

/* Enable internal pull-up for the selected CAN pins */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAPUD.bit.GPIO30 = 0; // Enable pull-up for GPIO30 (CANRXA)

// GpioCtrlRegs.GPAPUD.bit.GPIO18 = 0; // Enable pull-up for GPIO18 (CANRXA)

GpioCtrlRegs.GPAPUD.bit.GPIO31 = 0; // Enable pull-up for GPIO31 (CANTXA)

// GpioCtrlRegs.GPAPUD.bit.GPIO19 = 0; // Enable pull-up for GPIO19 (CANTXA)

/* Set qualification for selected CAN pins to asynch only */

// Inputs are synchronized to SYSCLKOUT by default.

// This will select asynch (no qualification) for the selected pins.

GpioCtrlRegs.GPAQSEL2.bit.GPIO30 = 3; // Asynch qual for GPIO30 (CANRXA)

// GpioCtrlRegs.GPAQSEL2.bit.GPIO18 = 3; // Asynch qual for GPIO18 (CANRXA)

/* Configure eCAN-A pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be eCAN functional pins.

GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 1; // Configure GPIO30 for CANRXA operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO18 = 3; // Configure GPIO18 for CANRXA operation

GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 1; // Configure GPIO31 for CANTXA operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO19 = 3; // Configure GPIO19 for CANTXA operation

EDIS;

}

#if (DSP28_ECANB)

void InitECanbGpio(void)

{

EALLOW;

/* Enable internal pull-up for the selected CAN pins */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAPUD.bit.GPIO8 = 0; // Enable pull-up for GPIO8 (CANTXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO12 = 0; // Enable pull-up for GPIO12 (CANTXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO16 = 0; // Enable pull-up for GPIO16 (CANTXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO20 = 0; // Enable pull-up for GPIO20 (CANTXB)

GpioCtrlRegs.GPAPUD.bit.GPIO10 = 0; // Enable pull-up for GPIO10 (CANRXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO13 = 0; // Enable pull-up for GPIO13 (CANRXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO17 = 0; // Enable pull-up for GPIO17 (CANRXB)

// GpioCtrlRegs.GPAPUD.bit.GPIO21 = 0; // Enable pull-up for GPIO21 (CANRXB)

/* Set qualification for selected CAN pins to asynch only */

// Inputs are synchronized to SYSCLKOUT by default.

// This will select asynch (no qualification) for the selected pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAQSEL1.bit.GPIO10 = 3; // Asynch qual for GPIO10 (CANRXB)

// GpioCtrlRegs.GPAQSEL1.bit.GPIO13 = 3; // Asynch qual for GPIO13 (CANRXB)

// GpioCtrlRegs.GPAQSEL2.bit.GPIO17 = 3; // Asynch qual for GPIO17 (CANRXB)

// GpioCtrlRegs.GPAQSEL2.bit.GPIO21 = 3; // Asynch qual for GPIO21 (CANRXB)

/* Configure eCAN-B pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be eCAN functional pins.

GpioCtrlRegs.GPAMUX1.bit.GPIO8 = 2; // Configure GPIO8 for CANTXB operation

// GpioCtrlRegs.GPAMUX1.bit.GPIO12 = 2; // Configure GPIO12 for CANTXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO16 = 2; // Configure GPIO16 for CANTXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO20 = 3; // Configure GPIO20 for CANTXB operation

GpioCtrlRegs.GPAMUX1.bit.GPIO10 = 2; // Configure GPIO10 for CANRXB operation

// GpioCtrlRegs.GPAMUX1.bit.GPIO13 = 2; // Configure GPIO13 for CANRXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO17 = 2; // Configure GPIO17 for CANRXB operation

// GpioCtrlRegs.GPAMUX2.bit.GPIO21 = 3; // Configure GPIO21 for CANRXB operation

EDIS;

}

#endif // if DSP28_ECANB

/*

Note: Bit timing parameters must be chosen based on the network parameters such

as the sampling point desired and the propagation delay of the network.

The propagation delay is a function of length of the cable, delay introduced by

the transceivers and opto/galvanic-isolators (if any).

The parameters used in this file must be changed taking into account the above

mentioned factors in order to arrive at the bit-timing parameters suitable

for a network.

*/

// TI File $Revision: /main/9 $

// Checkin $Date: July 2, 2008 14:31:12 $

//###########################################################################

//

// FILE: DSP2833x_Examples.h

//

// TITLE: DSP2833x Device Definitions.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

#ifndef DSP2833x_EXAMPLES_H

#define DSP2833x_EXAMPLES_H

#ifdef __cplusplus

extern "C" {

#endif

/*-----------------------------------------------------------------------------

Specify the PLL control register (PLLCR) and divide select (DIVSEL) value.

-----------------------------------------------------------------------------*/

//#define DSP28_DIVSEL 0 // Enable /4 for SYSCLKOUT

//#define DSP28_DIVSEL 1 // Enable /4 for SYSCKOUT

#define DSP28_DIVSEL 2 // Enable /2 for SYSCLKOUT

//#define DSP28_DIVSEL 3 // Enable /1 for SYSCLKOUT

#define DSP28_PLLCR 10

//#define DSP28_PLLCR 9

//#define DSP28_PLLCR 8

//#define DSP28_PLLCR 7

//#define DSP28_PLLCR 6

//#define DSP28_PLLCR 5

//#define DSP28_PLLCR 4

//#define DSP28_PLLCR 3

//#define DSP28_PLLCR 2

//#define DSP28_PLLCR 1

//#define DSP28_PLLCR 0 // PLL is bypassed in this mode

//----------------------------------------------------------------------------

/*-----------------------------------------------------------------------------

Specify the clock rate of the CPU (SYSCLKOUT) in nS.

Take into account the input clock frequency and the PLL multiplier

selected in step 1.

Use one of the values provided, or define your own.

The trailing L is required tells the compiler to treat

the number as a 64-bit value.

Only one statement should be uncommented.

Example 1:150 MHz devices:

CLKIN is a 30MHz crystal.

In step 1 the user specified PLLCR = 0xA for a

150Mhz CPU clock (SYSCLKOUT = 150MHz).

In this case, the CPU_RATE will be 6.667L

Uncomment the line: #define CPU_RATE 6.667L

Example 2: 100 MHz devices:

CLKIN is a 20MHz crystal.

In step 1 the user specified PLLCR = 0xA for a

100Mhz CPU clock (SYSCLKOUT = 100MHz).

In this case, the CPU_RATE will be 10.000L

Uncomment the line: #define CPU_RATE 10.000L

-----------------------------------------------------------------------------*/

#define CPU_RATE 6.667L // for a 150MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 7.143L // for a 140MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 8.333L // for a 120MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 10.000L // for a 100MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 13.330L // for a 75MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 20.000L // for a 50MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 33.333L // for a 30MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 41.667L // for a 24MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 50.000L // for a 20MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 66.667L // for a 15MHz CPU clock speed (SYSCLKOUT)

//#define CPU_RATE 100.000L // for a 10MHz CPU clock speed (SYSCLKOUT)

//----------------------------------------------------------------------------

/*-----------------------------------------------------------------------------

Target device (in DSP2833x_Device.h) determines CPU frequency

(for examples) - either 150 MHz (for 28335 and 28334) or 100 MHz

(for 28332). User does not have to change anything here.

-----------------------------------------------------------------------------*/

#if DSP28_28332 // DSP28_28332 device only

#define CPU_FRQ_100MHZ 1 // 100 Mhz CPU Freq (20 MHz input freq)

#define CPU_FRQ_150MHZ 0

#else

#define CPU_FRQ_100MHZ 0 // DSP28_28335||DSP28_28334

#define CPU_FRQ_150MHZ 1 // 150 MHz CPU Freq (30 MHz input freq) by DEFAULT

#endif

//---------------------------------------------------------------------------

// Include Example Header Files:

//

#include "DSP2833x_GlobalPrototypes.h" // Prototypes for global functions within the

// .c files.

#include "DSP2833x_ePwm_defines.h" // Macros used for PWM examples.

#include "DSP2833x_Dma_defines.h" // Macros used for DMA examples.

#include "DSP2833x_I2C_defines.h" // Macros used for I2C examples.

#define PARTNO_28335 0xEF

#define PARTNO_28334 0xEE

#define PARTNO_28332 0xED

#define PARTNO_28235 0xE8

#define PARTNO_28234 0xE7

#define PARTNO_28232 0xE6

// Include files not used with DSP/BIOS

#ifndef DSP28_BIOS

#include "DSP2833x_DefaultISR.h"

#endif

// DO NOT MODIFY THIS LINE.

#define DELAY_US(A) DSP28x_usDelay(((((long double) A * 1000.0L) / (long double)CPU_RATE) - 9.0L) / 5.0L)

#ifdef __cplusplus

}

#endif /* extern "C" */

#endif // end of DSP2833x_EXAMPLES_H definition

//===========================================================================

// End of file.

//===========================================================================