Dear All,

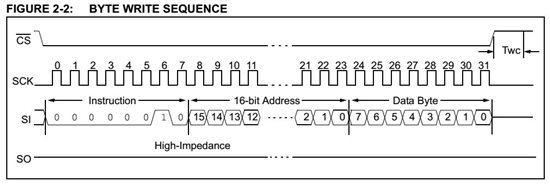

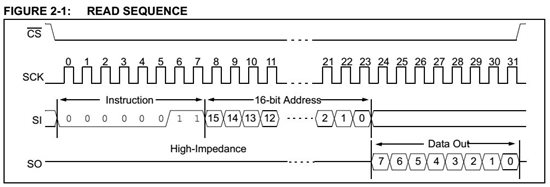

I am willing to interface an EEPROM to Piccolo F28069. I could not manage to send >16 bits over SPI link, with a single SPISTE pulse to the Slave. To describe it clearly, my memory device (e2prom) requires this command to be issued:

Could anyone advise, how to send this 32bit data in required format?

Regards,

Adnan Kurt