Champs,

I asked this for a key customer.

On F2837x,

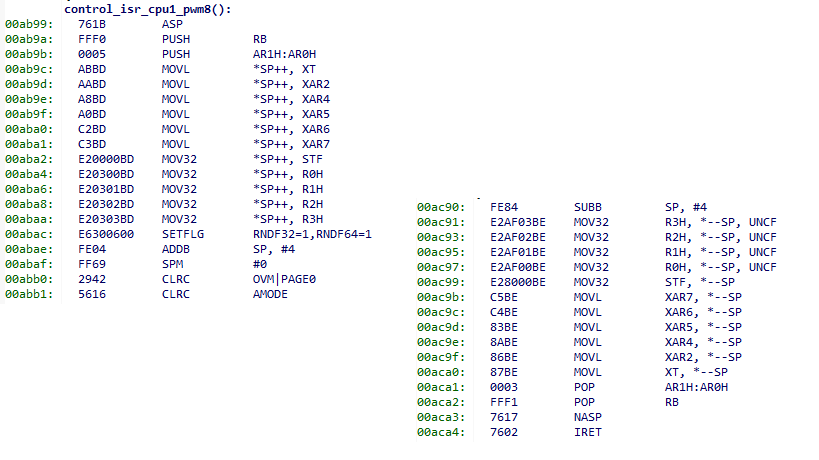

This is the diassembly codes of the customer's critical ISR code by C compiler for context save (top left) and context restore (bottom right).

Based on these codes, it takes more than 30 cycles for context save/restore, is it right?

If we add 15-20 cycles of interrupt latency (from the event trigger to entry of the ISR), then there should be at least 20+30 = 50 cycles used in this ISR for interrupt latency, context save/restore.

Is my understanding right?

This should be limited to the architecture of C28x, right?

Is it possible to significantly reduce the context save/restore cycles without resorting to assembly manually?

(That is, use C compiler only)

Wayne Huang