Other Parts Discussed in Thread: TMS320F28377S, CONTROLSUITE

Tool/software: Code Composer Studio

Hello folks,

i´m about to use the CLA on the TMS320F28377S which is mounted on the launchpad. I´m running CCS V.6

The point is, i can´t really figure out how to use the CLA. My goal is to write C Code for the CLA.

1.) There is a C-Compiler for the CLA which belongs to the the Code generation tools?

2.) Where do i write the Code which is supposed to be loaded into the CLA?

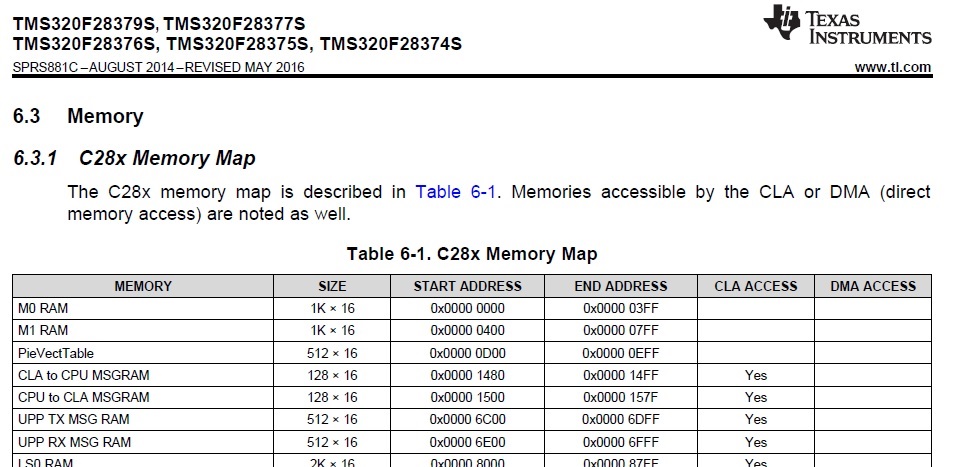

2.1.) From what i understood is, that CLA code is loaded together with the CPU code to the FLASH and then copied into the the RAM of the CLA?

2.2.) Do i write CLA code in the same source files from the CPU? If so, how does the envoironment know, which code has to be compiled for CPU and which for CLA? Since i read about .cla files, i think C Code for CLA is found in it´s own files? How would a "C source .cla file look like? Can i access Peripheral registers following the "register access approach" like "adcRes = AdcaResultRegs.ADCRESULT0;"

3.) Where do the references of "extern uint32_t Cla1funcsRunStart, Cla1funcsLoadStart, Cla1funcsLoadSize;" come from? Are they user defined or allready existing in library headers? What are thier exact purpose ( i can imagine they deal around to map the CLA code).

best regards,

Jasson