Hi all,

I try to implement peak current mode control with the TMS320F28379D.

A 1V signal is applied to the CMPIN1P Pin. The ramp generator is used on the negative input of the comparator. The CMPSS Module 1 is configured with the following code:

CMPSS_enableModule(CMPSS1_BASE);

CMPSS_configHighComparator(CMPSS1_BASE, CMPSS_INSRC_DAC);

CMPSS_configDAC(CMPSS1_BASE, CMPSS_DACVAL_PWMSYNC |

CMPSS_DACREF_VDDA |

CMPSS_DACSRC_RAMP);

CMPSS_configOutputsHigh(CMPSS1_BASE, CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_SYNC_COMP);

CMPSS_setRampDecValue(CMPSS1_BASE, RAMP_DECREMENT);

CMPSS_setRampDelayValue(CMPSS1_BASE, RAMP_DELAY);

CMPSS_configRamp(CMPSS1_BASE,

27000,

RAMP_DECREMENT,

RAMP_DELAY,

1,

true);

CMPSS_configFilterHigh(CMPSS1_BASE, 2, 20, 15);

CMPSS_initFilterHigh(CMPSS1_BASE);

GPIO_setMasterCore(11, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_11_OUTPUTXBAR7);

GPIO_setDirectionMode(11, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(11, GPIO_PIN_TYPE_STD);

XBAR_setOutputMuxConfig(XBAR_OUTPUT7, XBAR_OUT_MUX00_CMPSS1_CTRIPOUTH);

XBAR_enableOutputMux(XBAR_OUTPUT7, XBAR_MUX00);

XBAR_setEPWMMuxConfig(XBAR_TRIP4, XBAR_EPWM_MUX00_CMPSS1_CTRIPH);

XBAR_enableEPWMMux(XBAR_TRIP4, XBAR_MUX00);

This works as expected.

Now there are two options to configure the ePWM module.

Option1: The traditional way using the Trip Zone, same as with the old ePWM Type 1

// Set-up TBCLK

EPWM_setTimeBasePeriod(EPWM1_BASE, PWM_TIMER_TBPRD);

EPWM_setPhaseShift(EPWM1_BASE, 0);

EPWM_setTimeBaseCounter(EPWM1_BASE, 0U);

EPWM_setSyncOutPulseMode(EPWM1_BASE, EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO);

// Set up counter mode

EPWM_setTimeBaseCounterMode(EPWM1_BASE, EPWM_COUNTER_MODE_UP);

EPWM_disablePhaseShiftLoad(EPWM1_BASE);

EPWM_setClockPrescaler(EPWM1_BASE,

EPWM_CLOCK_DIVIDER_1,

EPWM_HSCLOCK_DIVIDER_1);

// Set up shadowing

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE,

EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE,

EPWM_COUNTER_COMPARE_B,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

// Set Compare values

EPWM_setCounterCompareValue(EPWM1_BASE,

EPWM_COUNTER_COMPARE_A,

0);

// Set actions

EPWM_setActionQualifierAction(EPWM1_BASE,

EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(EPWM1_BASE,

EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

// Set Digital Compare

// TRIP4 -> DCBH

EPWM_enableDigitalCompareTripCombinationInput(EPWM1_BASE,

EPWM_DC_COMBINATIONAL_TRIPIN4,

EPWM_DC_TYPE_DCBH);

// DCBH -> DCBEVT2

EPWM_setTripZoneDigitalCompareEventCondition(EPWM1_BASE,

EPWM_TZ_DC_OUTPUT_B2,

EPWM_TZ_EVENT_DCXH_HIGH);

// Enable DCB as CBC

EPWM_enableTripZoneSignals(EPWM1_BASE, EPWM_TZ_SIGNAL_DCBEVT2);

// Set Trip Zone

EPWM_setTripZoneAction(EPWM1_BASE, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

This works as expected. When the Cmpss1Regs.RAMPMAXREFS value is increased linear from 0 to 40000, the PWM is low at the beginning and as soon as the ramp start value crosses the 1V small PWM pulses are generated.

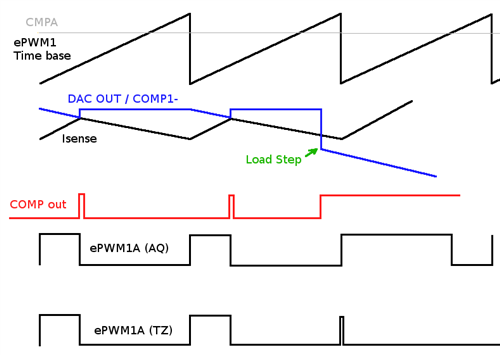

The scope shot shows the Duty Cycle rises from 0 to 25%. With the comparator pulse, the PWM turns low. Everything works as expected.

Footnote: PWM1_L is permanent low. This should be the inverted signal of PWM1_H, but is not possible with the DSP. The inversion and dead band will be generated externally with a hardware gate.

Option2: The new way using the Action Quallifier and the Dead Band

Instead of using the Trip Zone to clear the PWM signal the Action Qualifier is used. This has the advantage of generation the complementary PWM signal with the Dead Band module.

// Set-up TBCLK

EPWM_setTimeBasePeriod(EPWM1_BASE, PWM_TIMER_TBPRD);

EPWM_setTimeBaseCounter(EPWM1_BASE, 0U);

EPWM_setSyncOutPulseMode(EPWM1_BASE, EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO);

// Set up counter mode

EPWM_setTimeBaseCounterMode(EPWM1_BASE, EPWM_COUNTER_MODE_UP);

EPWM_disablePhaseShiftLoad(EPWM1_BASE);

EPWM_setClockPrescaler(EPWM1_BASE,

EPWM_CLOCK_DIVIDER_1,

EPWM_HSCLOCK_DIVIDER_1);

// Set up shadowing

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE,

EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE,

EPWM_COUNTER_COMPARE_B,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

// Set Compare values

EPWM_setCounterCompareValue(EPWM1_BASE,

EPWM_COUNTER_COMPARE_A,

0);

// Set Deadband

EPWM_setDeadBandDelayPolarity(EPWM1_BASE, EPWM_DB_FED, EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_setDeadBandDelayMode(EPWM1_BASE, EPWM_DB_RED, true);

EPWM_setDeadBandDelayMode(EPWM1_BASE, EPWM_DB_FED, true);

EPWM_setRisingEdgeDelayCount(EPWM1_BASE, PWM_DB);

EPWM_setFallingEdgeDelayCount(EPWM1_BASE, PWM_DB);

// Set actions

EPWM_setActionQualifierAction(EPWM1_BASE,

EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(EPWM1_BASE,

EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

// Set Digital Compare

// TRIP4 -> DCBH

EPWM_enableDigitalCompareTripCombinationInput(EPWM1_BASE,

EPWM_DC_COMBINATIONAL_TRIPIN4,

EPWM_DC_TYPE_DCBH);

// DCBH -> DCBEVT2

EPWM_setTripZoneDigitalCompareEventCondition(EPWM1_BASE,

EPWM_TZ_DC_OUTPUT_B2,

EPWM_TZ_EVENT_DCXH_HIGH);

// Enable DCB as T1 Source

EPWM_setActionQualifierT1TriggerSource(EPWM1_BASE, EPWM_AQ_TRIGGER_EVENT_TRIG_DCB_2);

EPWM_setActionQualifierAction(EPWM1_BASE,

EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_T1_COUNT_UP);

The COMPSS1 initialization code is the same as with the option 1.

With this implementation, I have two unexpected behavior.

1: When the Ramp Start Value is below the 1V of the negative Input of the comparator, why is the duty cycle at 50% (this is the value of CMPA). My understanding is, it should be 0.

2: The Dead Band module is not generating the inverted gate signal. The Dead Band module should be independent of the Action Qualifier module.

Regards,

Tobias