Part Number: TMS320F28377D

Other Parts Discussed in Thread: AMC1306EVM, C2000WARE, AMC1306E25, AMC1311

Tool/software: Code Composer Studio

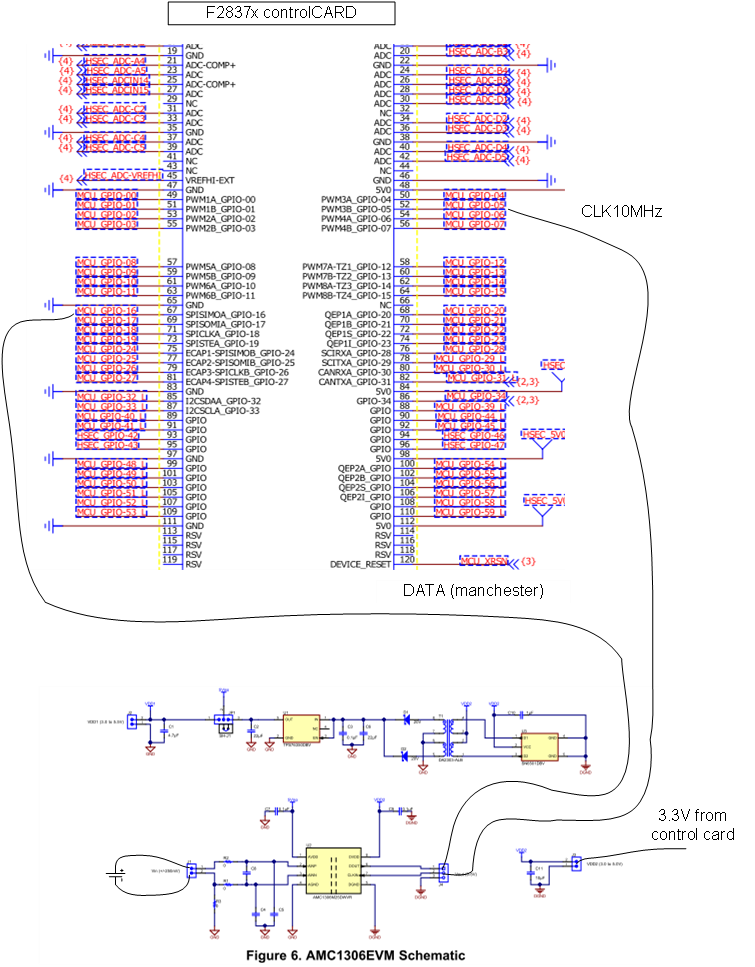

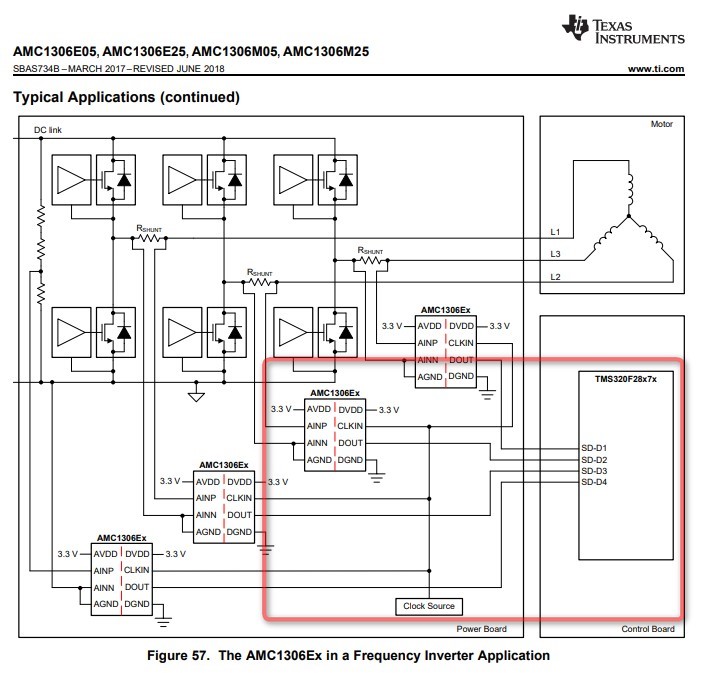

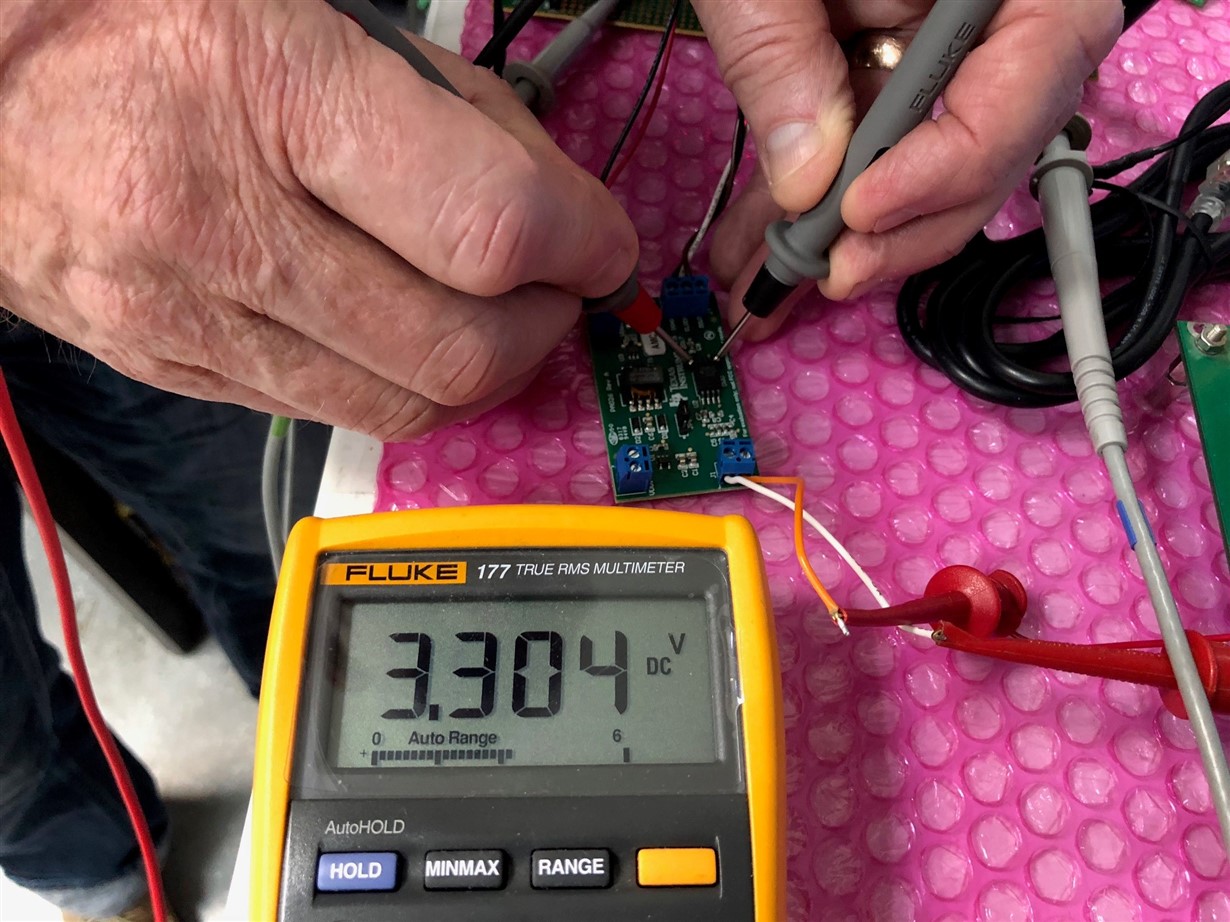

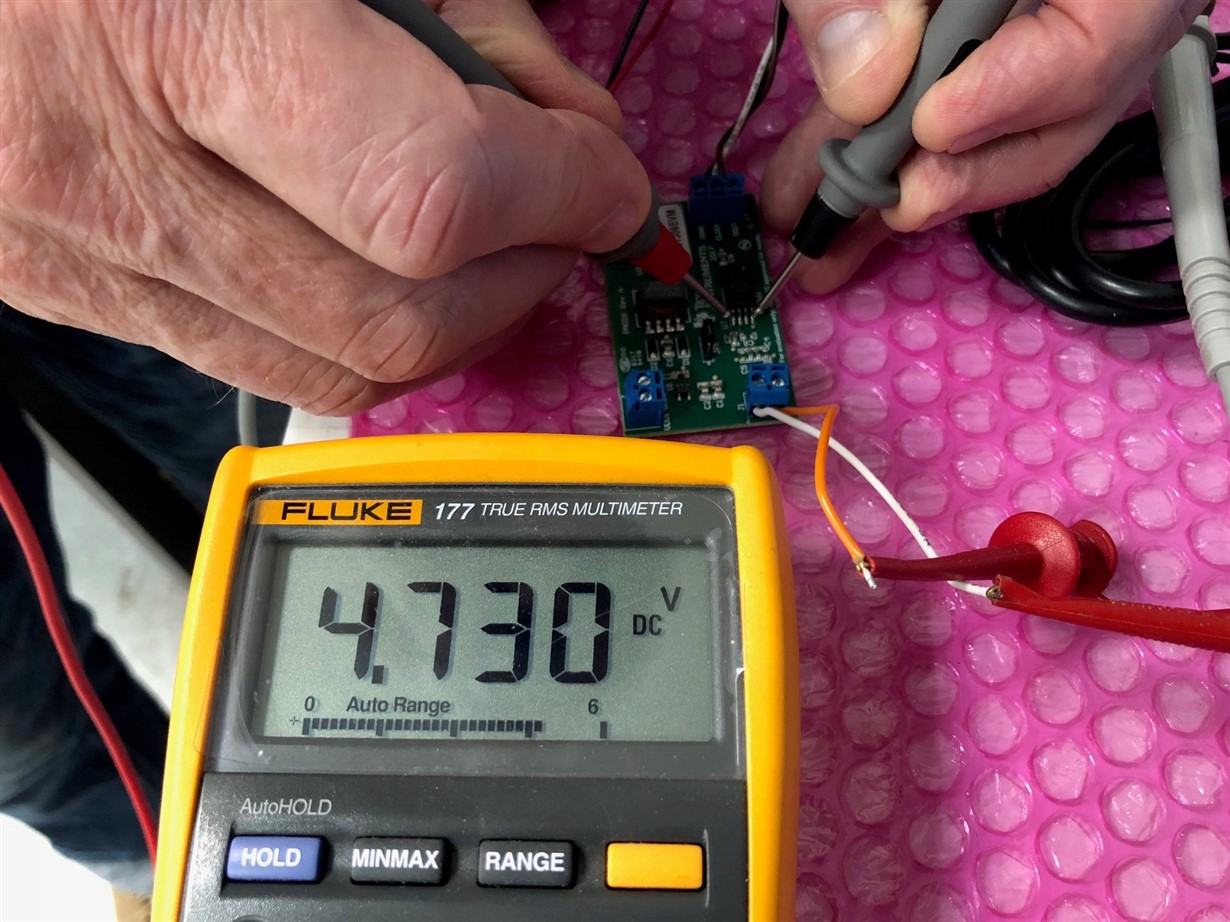

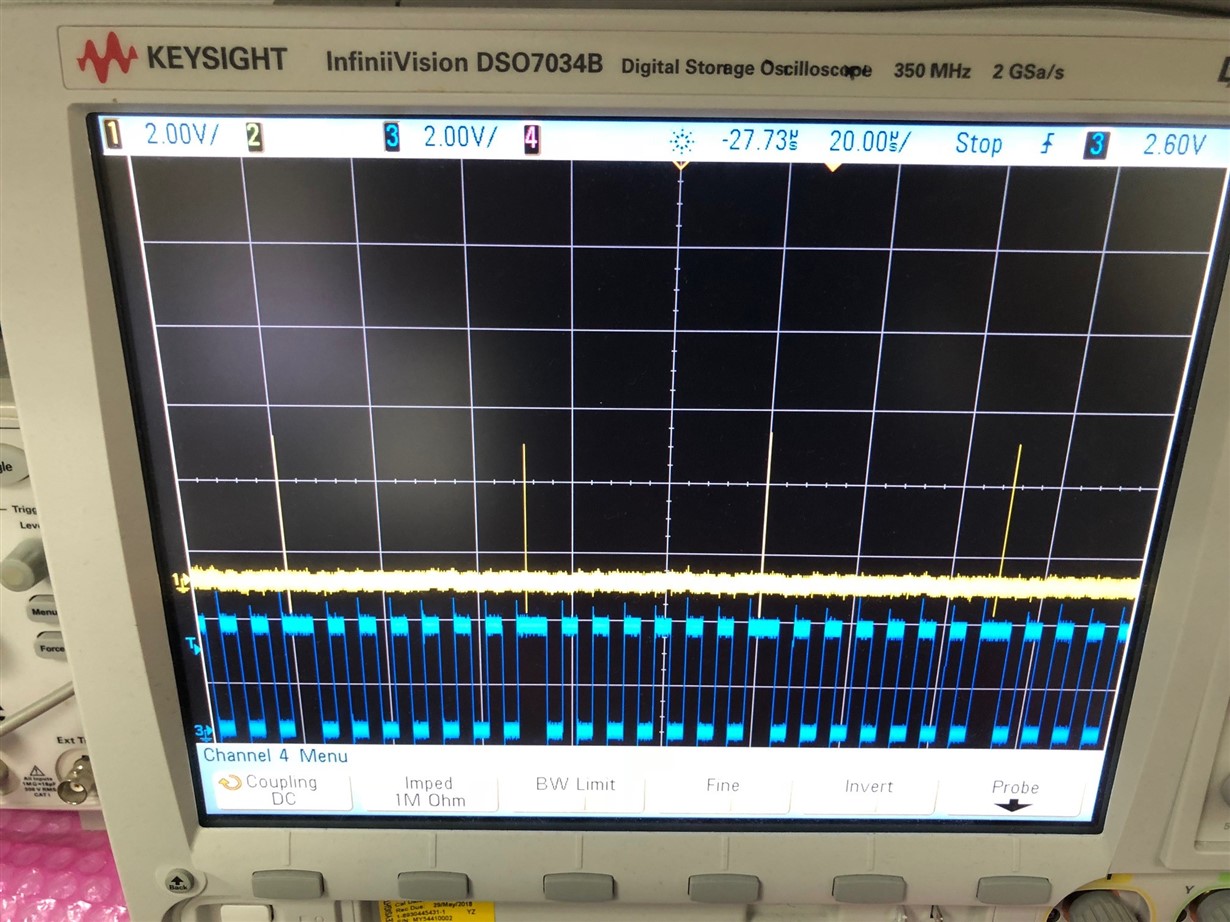

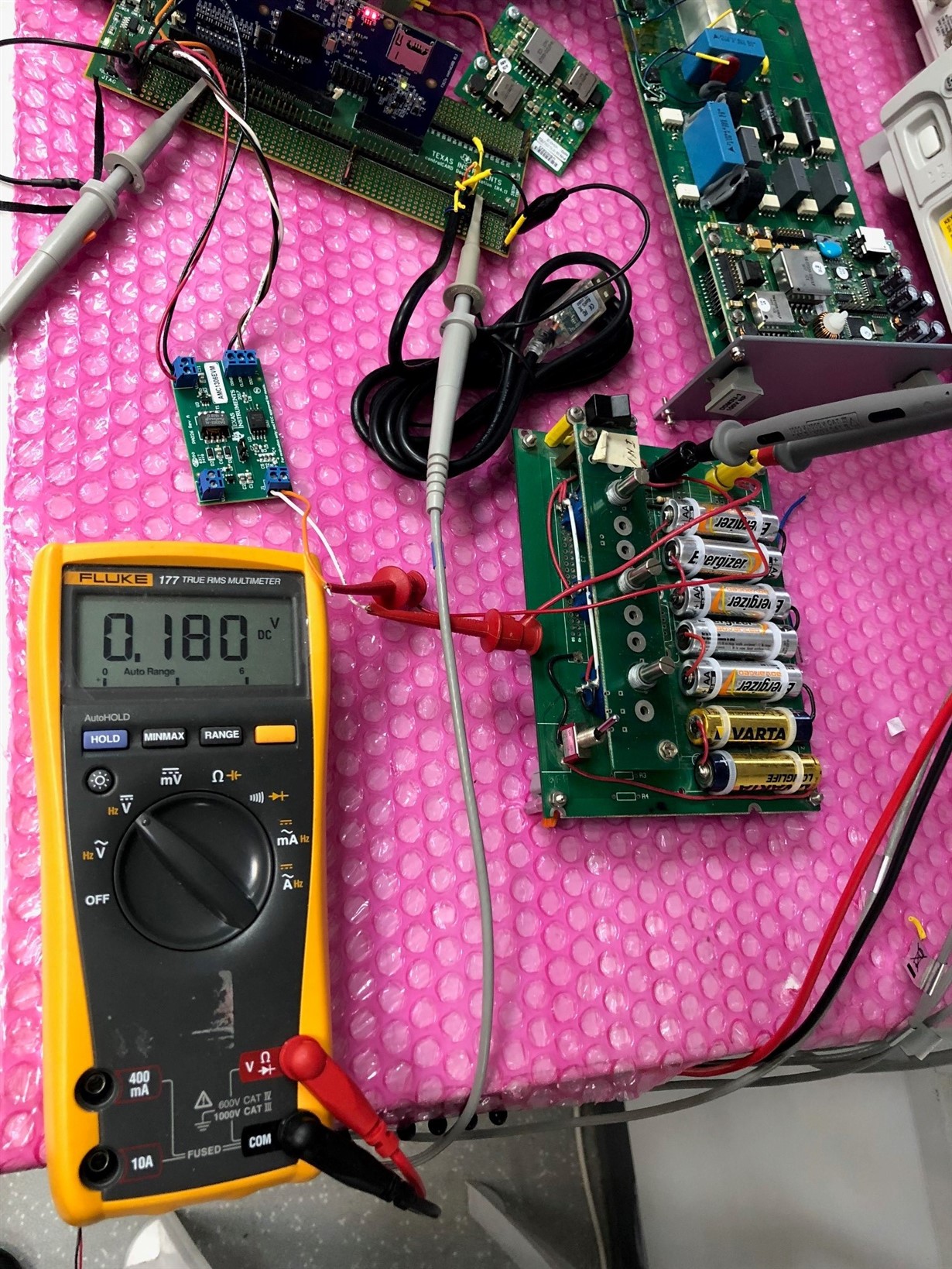

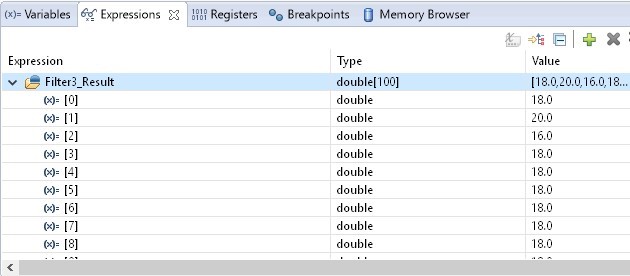

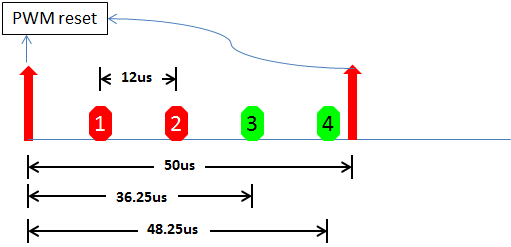

I’m trying to configure the Delfino F2837xS CPU with AMC1306EVM Sigma-Delta module configured for Manchester encoding. I’ve successfully received the 16-bit data from the SDFM, and the data is consistent. My current problem is the values I receive.

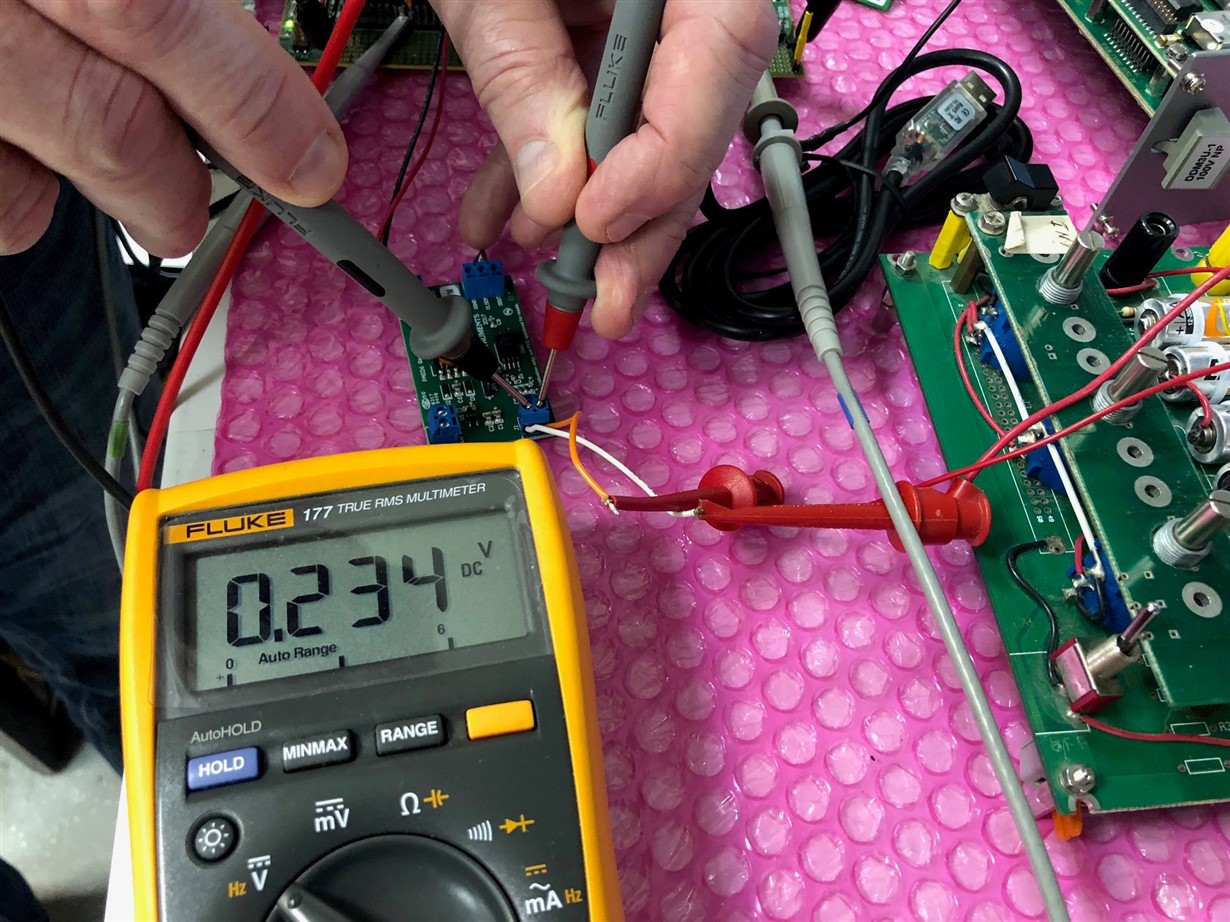

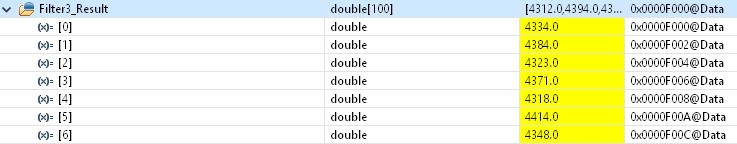

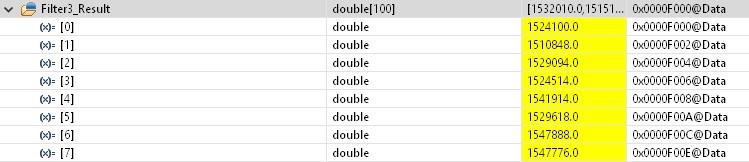

When supplying 250 mV, I read from SDFM only about 4400, which is a lot less than expected, since it’s 16-bit signed value with values up to 32768, and since I supply values close to the maximum supported by the evaluation board, I would expect output close to available maximum as well. (Manchester encoding is not the one that causes the problem here; I've achieved the same results with Mode_0). Same happens with negative values; I supply -250 mV and receive a negative number close to -4400. The results are consistent; if I supply voltage between -250 mV and +250 mV, I receive output between -4400 and +4400, proportionally. If the input voltage is out of the [-250; +250] scope, the output grows proportionally with higher inaccurancy, until I leave the [-320; +320] mVolts range of the evaluation board.

I have forged a simple proportion and successfully interpret the value I read into mVolts, it gives readings that fall close to the actual supplied voltage. But the range [-4400; +4400] I receive from the DSP’s SDFM is too coarse for fine current measurement, and small differences in the DSP’s SDFM output result in error of ±5 mV after the interpretation. In other words, for input of 100 mV I receive values that fall between 95 and 105 mV in Gauss’ bell. This noise is not a result of the input; it happens even when the input is short-circuited and gives strict 0. The wires are short and checked for external interference. Anyway, the ±5 mV difference would be way over the noise ratio.

The formula I forged is mVolts = 320.0 * (SDFM_output - 50.0) / 5250 for positive input (for negatives it's a bit different). As I said, it works relatively well, save for the ±5 mV error.

On the other hand, when using the formulae received from TI and not the one that follows from proportion, the output in mVolts don’t even fall close to the actual input. It comes out much lower than expected. (Just like the output from the Sigma-Delta filter is way lower than expected).

The formula I received is: Vin = 320.0 * { (2 x SDFM_output) / ((256 * 256 (for SINC1) ) - 1)}

Would you please advise on what could be done about the interpretation?