Part Number: TMS320F28379D

Other Parts Discussed in Thread: C2000WARE

Is it possible to configure the 4 16-bit ADCs of the TMS320F28379D to work as a single highspeed 4MSPS ADC (in interleaved mode)?

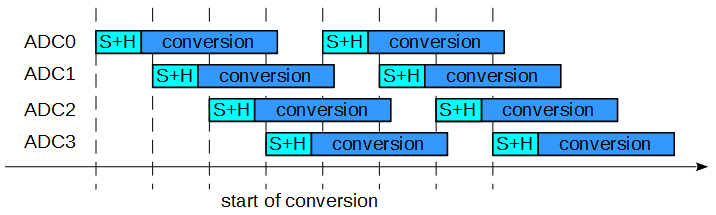

They would all be sampling the same input. When channel N completes S+H channel N+1 starts S+H in parallel with channel N continuing to perform the conversion.

Something like this: