In our project, we encounter an 28075 ePWM wave problem in September. We grabbed the waveform to prove that power module(half-bridge) would be damaged because of short through.

Original Question Link: e2e.ti.com/.../2705829

1. Problem phenomenon

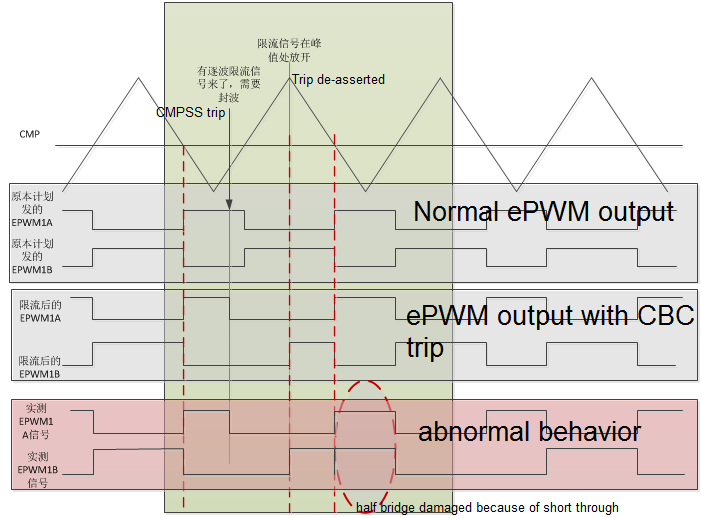

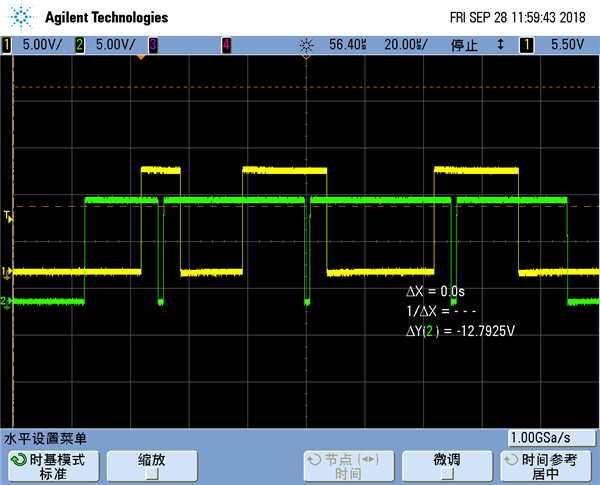

ePWM1A and ePWM1B were configured to complementary output. Ext SyncIn was connected to ePWM1A. CMPSS was used to trip the ePWM1 on a cycle-by-cycle basis. You can find the ePWM output waveforms we found. In the third waveform, ePWM1B cannot be cleared.

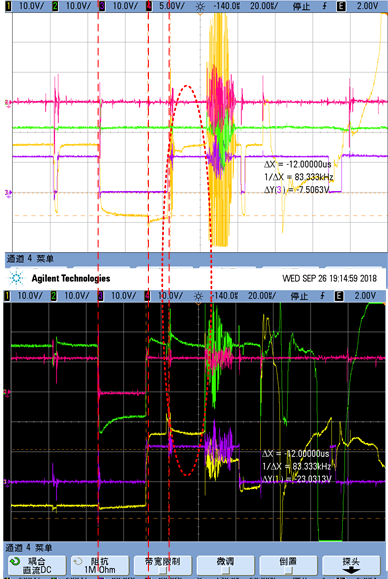

You can find their scope capture as follows. The purple waveform(CH3) in the first picture is ePWM1A, and the purple waveform(CH3) in the second picture is ePWM1B.

And there is no ePWM configuration again except the configuration(attached also) during initialization.

2. Some findings

Because of this problem, many of our machines are damaged. We did many experiments, and found some possible reasons.

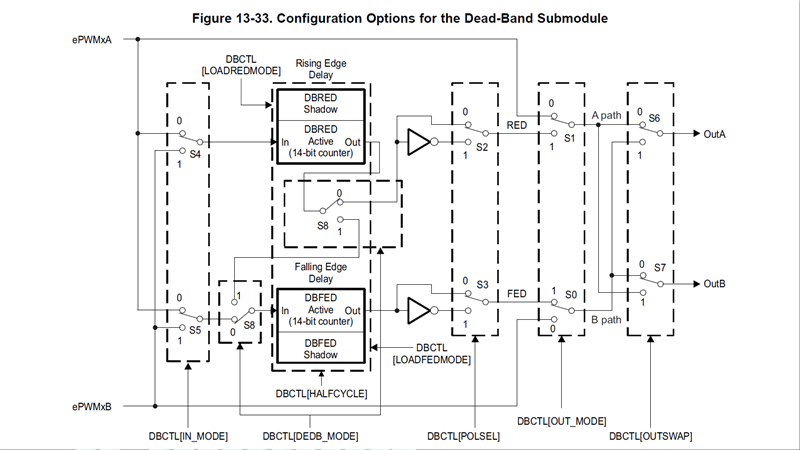

2.1 Input sources configuration of ePWM

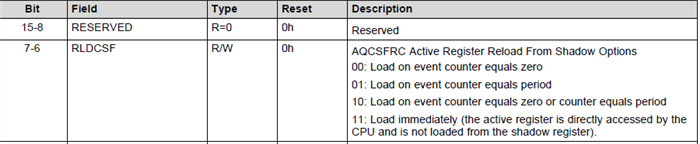

ePWMxA and ePWMxB are configured as two independent input sources in previous procedures based on f28075 datasheet.

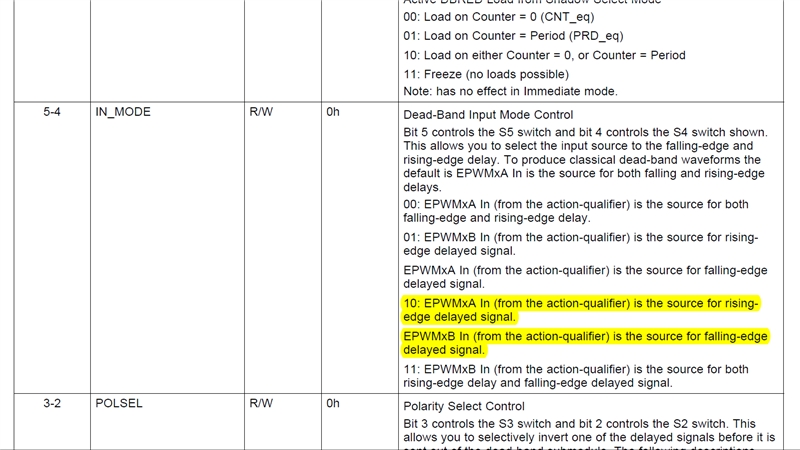

That is, EPwm1Regs.DBCTL.bit.IN_MODE = 0x2;

10: EPWMxA In (from the action-qualifier) is the source for risingedgedelayed signal.EPWMxB In (from the action-qualifier) is the source for falling-edge delayed signal.

So we assign values to CMPA and CMPB respectively in the last part of CLA, but they are executed one by one.

Such as:

EPwm1Regs.CMPA.bit.CMPA = INVThree_Output.fUpwmInv_A;

EPwm1Regs.CMPB.bit.CMPB = INVThree_Output.fUpwmInv_A;

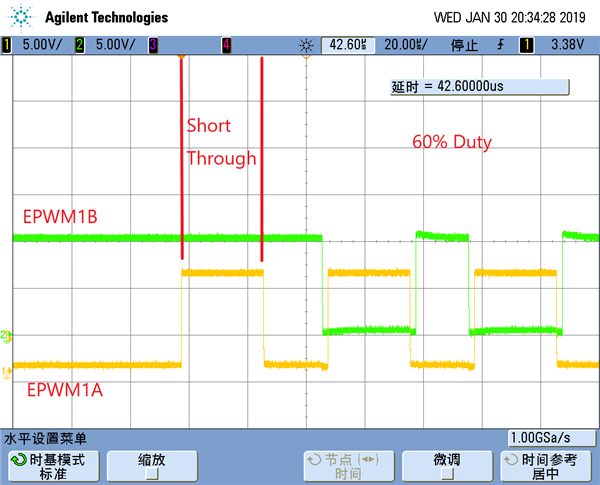

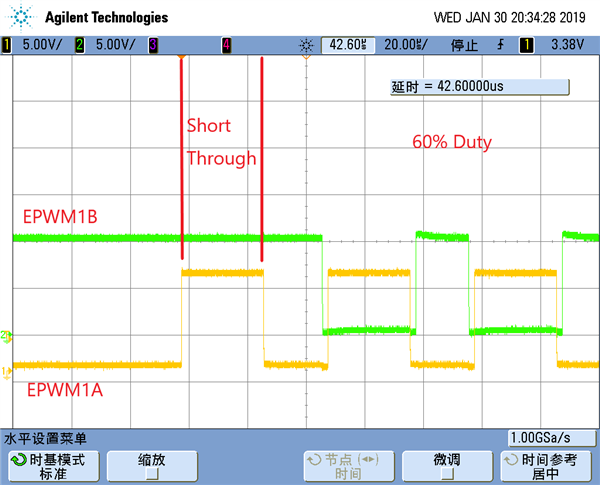

We conducted a simulation experiment, when CMPA executed the assignment statement, and CMPB did not execute the load statement, there will be a short through phenomenon. In the follow picture, CH1 is ePWM1A, and CH2 is ePWM1B.

Then, ePWMxA and ePWMxB are configured as only one source.

That is, EPwm1Regs.DBCTL.bit.IN_MODE = 0x0;

We repeated many experiments, and there was no abnormal or short through phenomenon. We have also confirmed that the CLA runtime meets the requirements.Due to project schedule, we took this modification measures.

Over the past two months, hundreds of machines have been running for a long time without any problems.

2. Ext SyncIn single

In the five experiments, we all grabbed the synchronous signal, and found no abnormal signal.

Because the reason for this problem is not clear, we can not use 28075 chip for the next project. At present, we have no idea about this problem. Would you kindly help to check the root cause of this issue?

Thanks.

Regards,

Jetfan