One of my important customer is designing digital power module using F28075. Now during their debugging, they found the power module(half-bridge) would be damaged because of short through. And they found the damage came from the complementary ePWM output signal was changed accidentally.

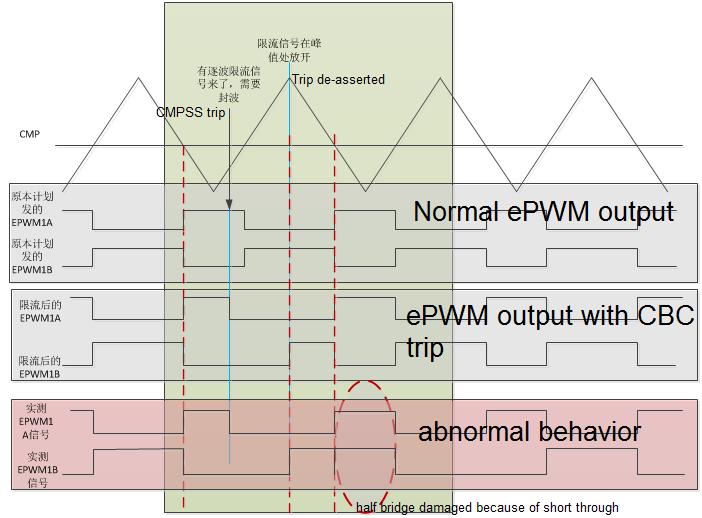

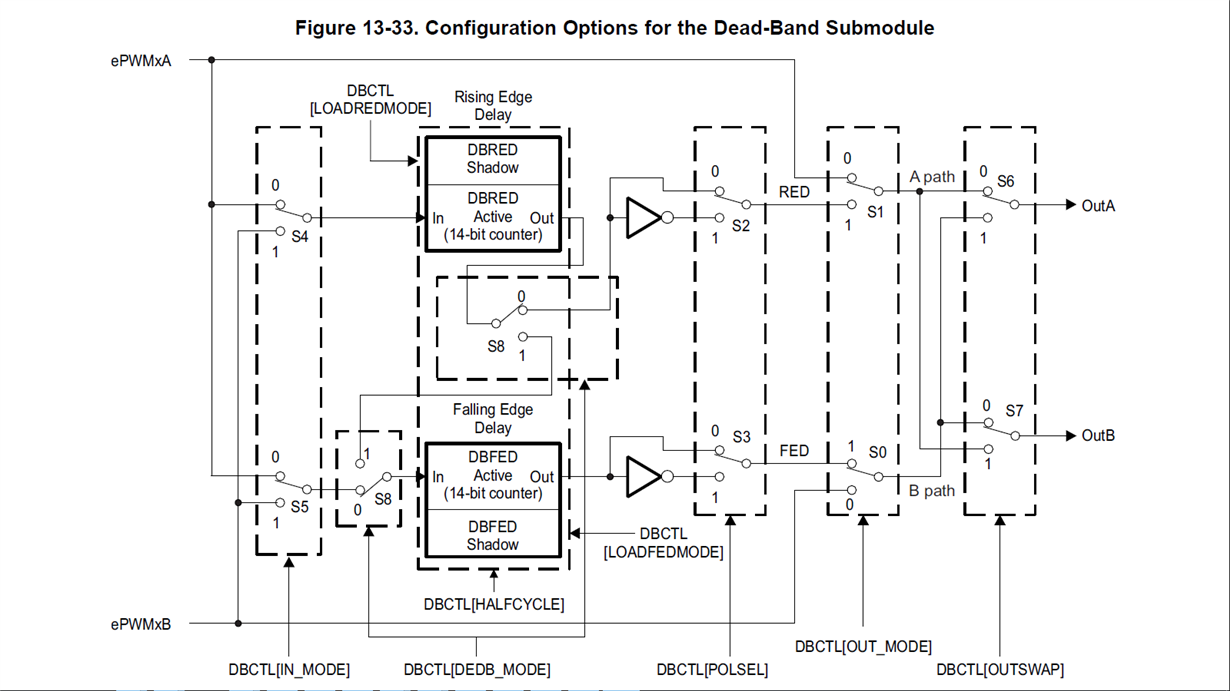

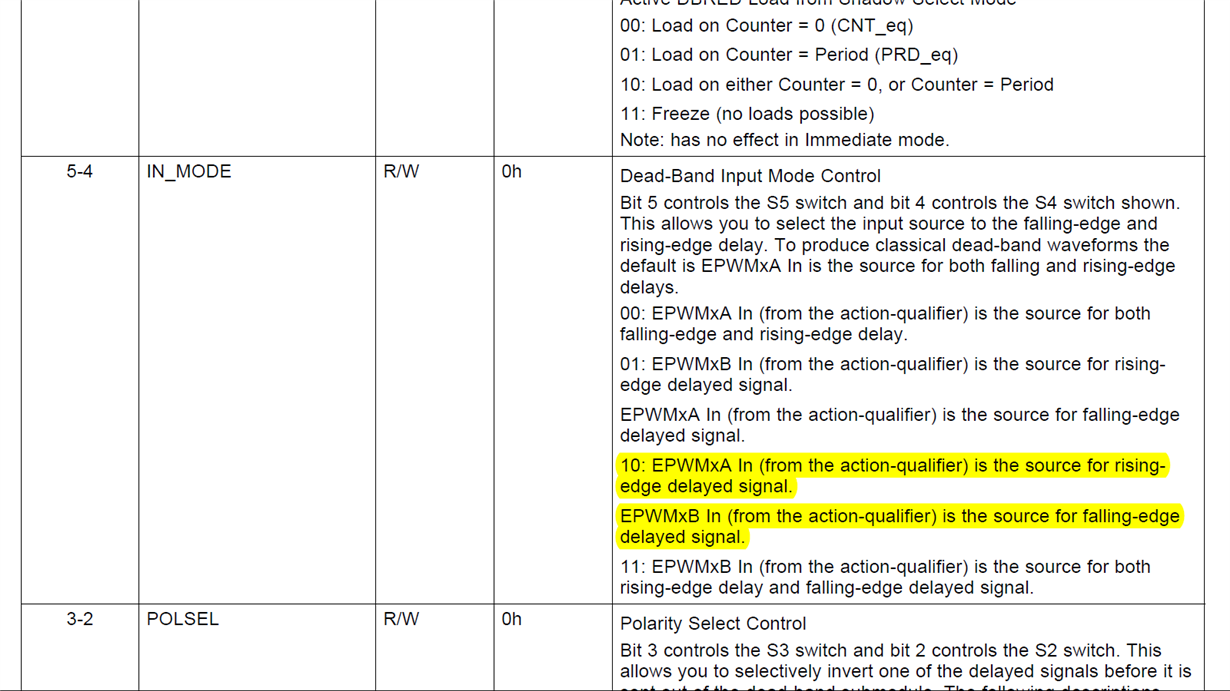

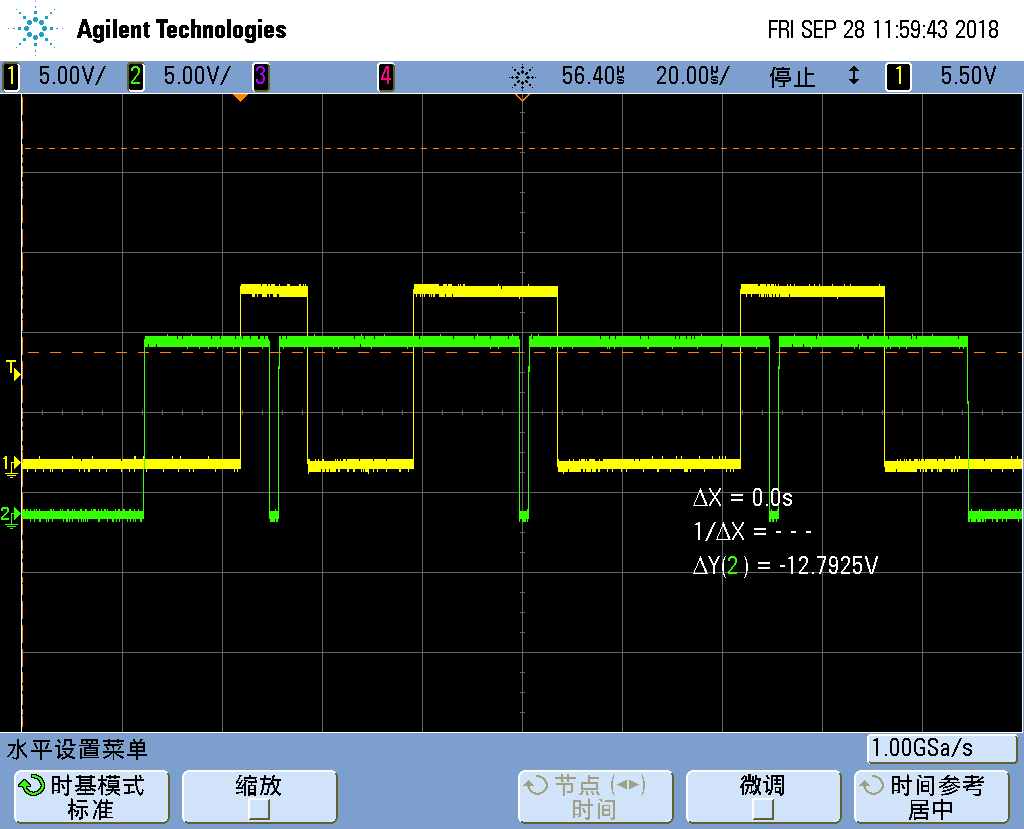

ePWM1A and ePWM1B were configured to complementary output. Ext SyncIn was connected to ePWM1A. CMPSS was used to trip the ePWM1 on a cycle-by-cycle basis. You can find the ePWM output waveforms they found. In the third waveform, ePWM1B cannot be cleared.

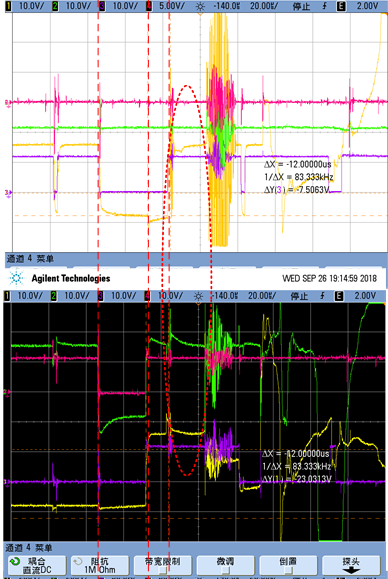

You can find their scope capture as follows. The purple waveform(CH3) in the first picture is ePWM1A, and the purple waveform(CH3) in the second picture is ePWM1B.

And there is no ePWM configuration again except the configuration(attached also) during initialization.

Would you kindly help to check the root cause of this issue?

Thanks.

Regards,

Young Hu