Team,

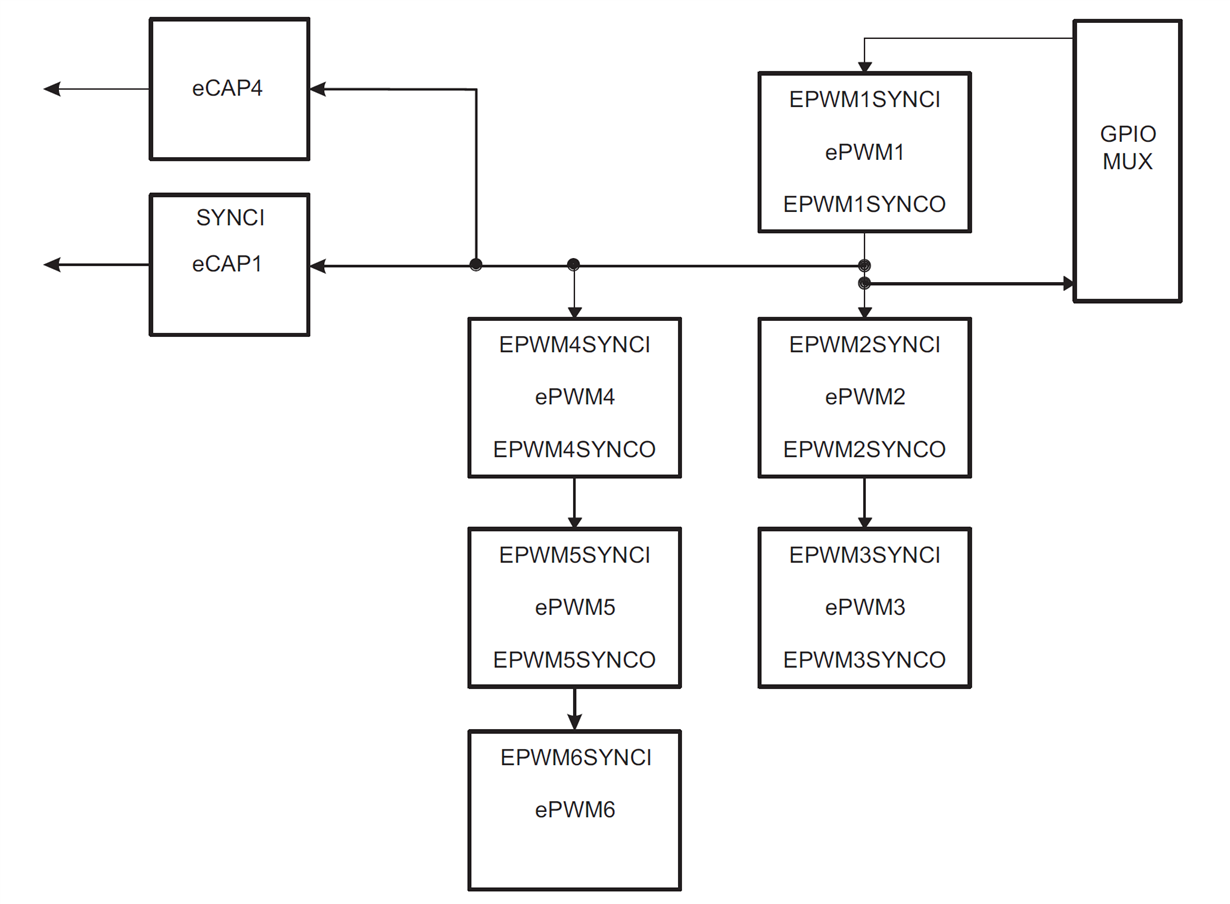

My customer has had his PWM modules linked together with the SYNC output of PWM1 provided to PWM2 – PWM6 through the master/slave PWM module configuration options. He is trying to break the link between modules 2 & 3 so that he can have the following daisy chains:

- PWM1 -> PWM2

- PWM3 -> PWM4 -> PWM5 -> PWM6

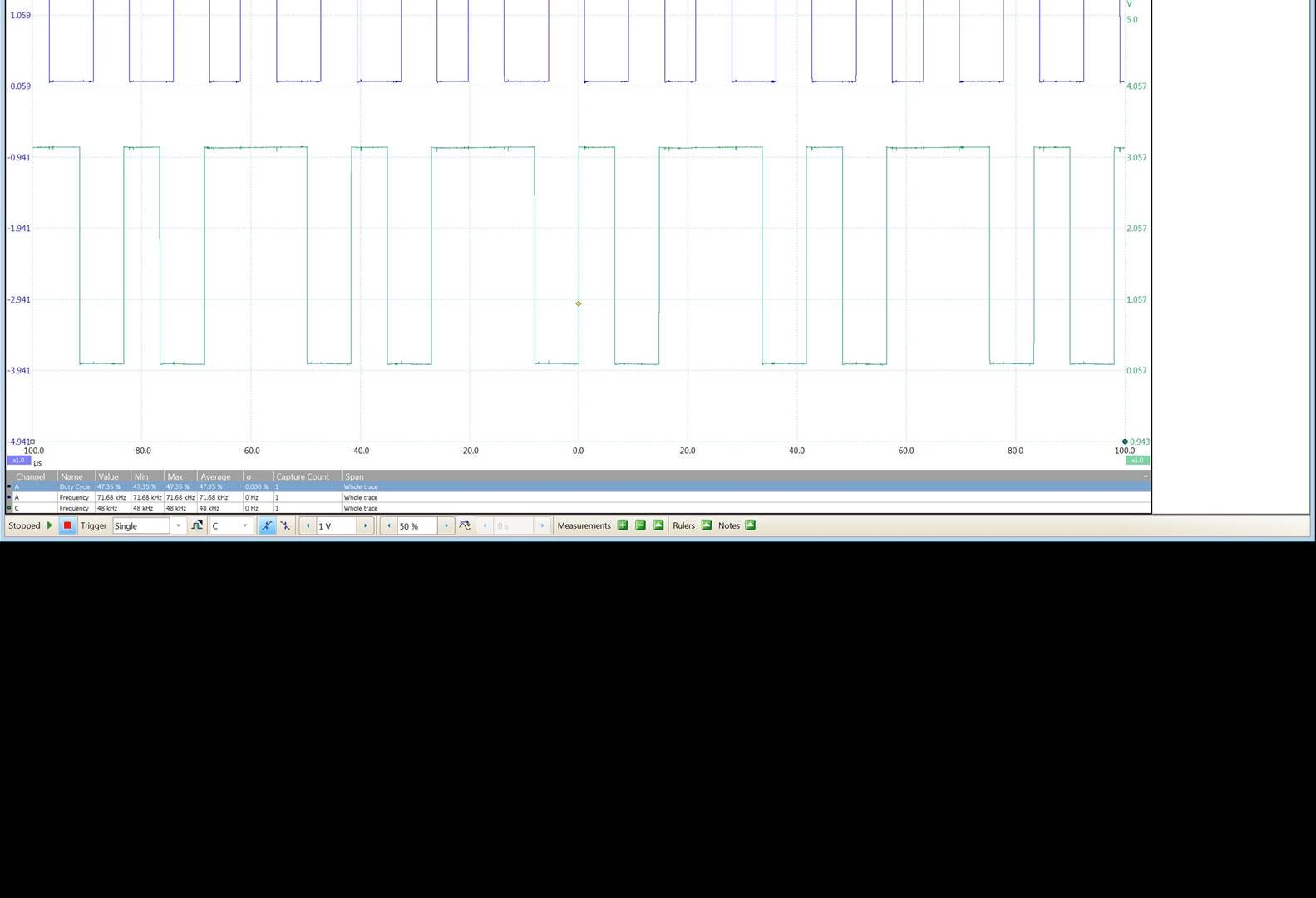

When customer tried setting EPwm3Regs.TBCTL.bit.PHSEN = TB_DISABLE he found that the CTR would pause at one count for a period of time on both the count up and count down. This is all using Matlab Simulink auto-generated code that is pulling in a custom C module to help with the configuration of the PWM. The PWM is also triggering an ISR that is used for calculation of all of the control code. There is some issue with the way that it is configured that is preventing him from achieving good operation when he does not link all the PWMs as a slave to PWM1.

See figure 51 - here: http://www.ti.com/lit/ug/sprug04a/sprug04a.pdf

Your inputs would be greatly appreciated.

Thanks!

Viktorija