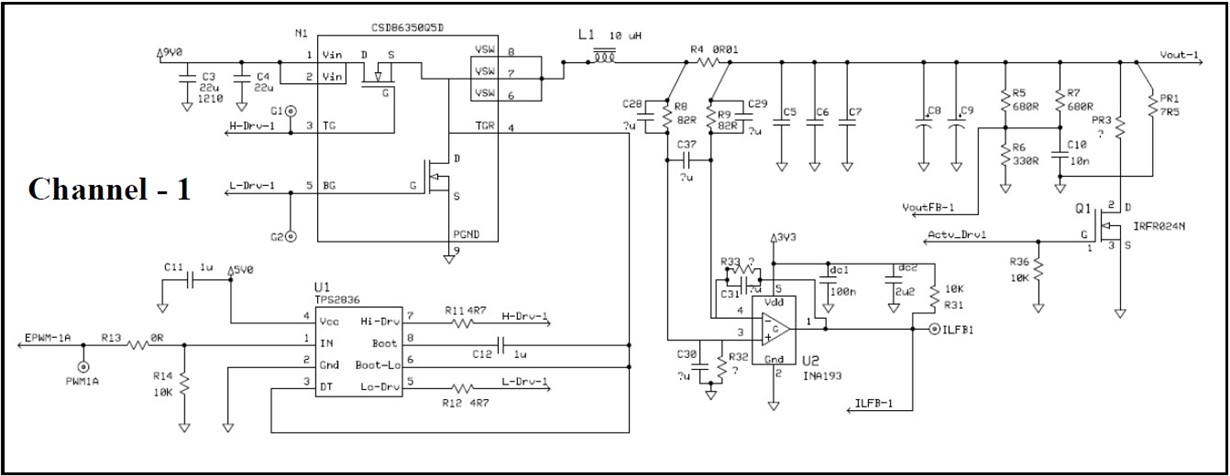

I have a question on lab 4 &5 example located at "C:\ti\DPS Workshop_release v2\Workshop\DPS_Workshop".

According to DPS Workshop Manual v1.2.pdf, delta Vc needs to design smaller than delta Vs to keep steady state output, no limit cycle.

However, I got confused when I substitute F28335 datasheet parameters into deltaVc&Vs calculation.

delta Vc= Input voltage / DPWM counts under switching frequency(200Khz) = (9V) / (300counts)=30mV

delta Vs=max ADC input voltage / 12 bits counts = (3.3V) / (2^12) =0.806 mV

Apparently, delta Vc is bigger than delta Vs here which may lead to limit cycle oscillation problem.

I really want to know which part of the code in the example project solve this LCO problem.

Figure below is the screenshot of the page describing limit cycle in DPS Workshop Manual v1.2.pdf.