Hi,

I am trying to run the example <C2000WAREINSTALLDIR>\device_support\f2837xd\examples\cpu1\hrpwm_deadband_sfo_v8 in CPU2. I am running GPIO initialization required for ePWM and allocating the ePWMs required to CPU2 in CPU1 as below

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

CpuSysRegs.PCLKCR2.bit.EPWM1 = 0;

CpuSysRegs.PCLKCR2.bit.EPWM2 = 0;

/* Assign used PWM modules to CPU2 */

DevCfgRegs.CPUSEL0.bit.EPWM1 = 1;

DevCfgRegs.CPUSEL0.bit.EPWM2 = 1;

EDIS;

InitEPwm1Gpio();

InitEPwm2Gpio();

Then I perform the rest of ePWM1 and ePWM2 configuration, setting up of ISR and modification of HR period, phase inside ISR in CPU2 after enabling the clock as below

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

CpuSysRegs.PCLKCR2.bit.EPWM1 = 1;

CpuSysRegs.PCLKCR2.bit.EPWM2 = 1;

EDIS;

//

// Init HRPWM1/HRPWM2

//

HRPWM1_Config(360);

HRPWM2_Config(360);

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Resync PWM timebase clock

(*ePWM[PWM1]).GLDCTL2.bit.OSHTLD = 1; // This should also write to

// GLDCTL2 of PWM2

EDIS;

//

// Configure ePWM1 to generate interrupts on period match

//

(*ePWM[PWM1]).ETSEL.bit.INTSEL = 1; // Interrupt on counter zero match

(*ePWM[PWM1]).ETSEL.bit.INTEN = 1; // Enable peripheral interrupt

(*ePWM[PWM1]).ETPS.bit.INTPRD = 1; // Generate interrupt on every event

PieCtrlRegs.PIEIER3.bit.INTx1 = 1; // Enable ePWM1 interrupt in PIE

IER |= 0x0004; // Enable core INT #3

EINT;

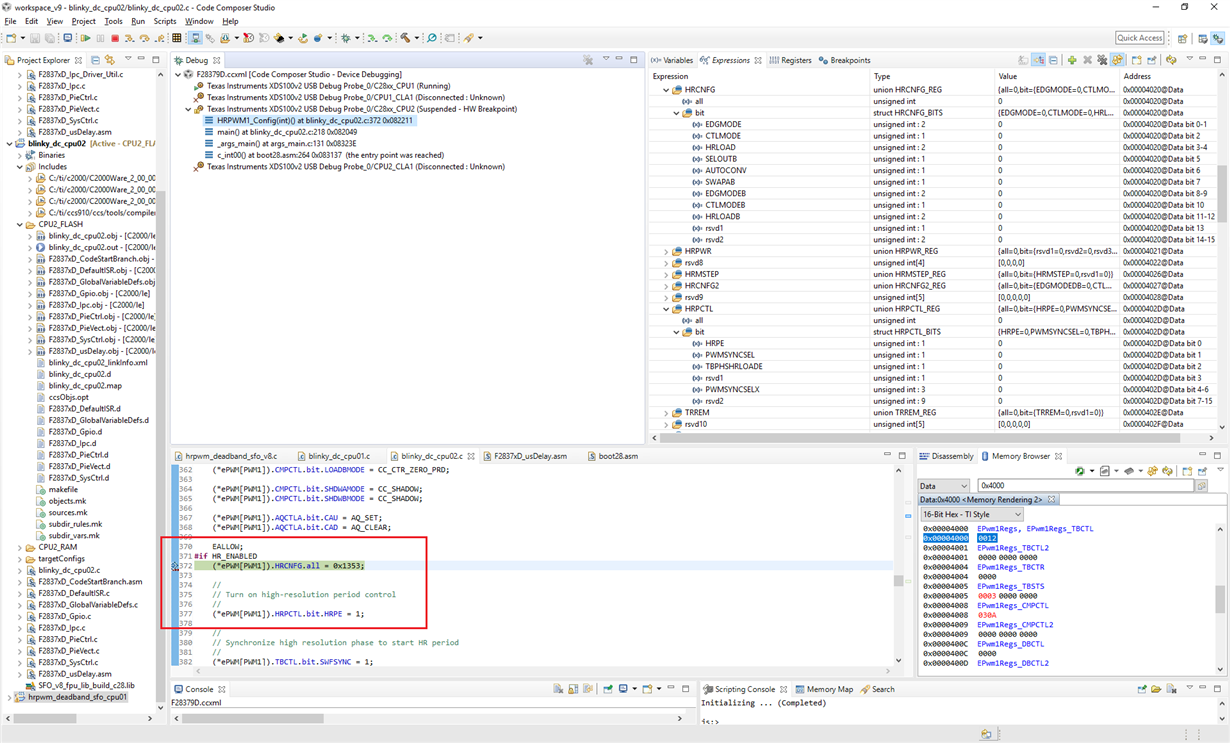

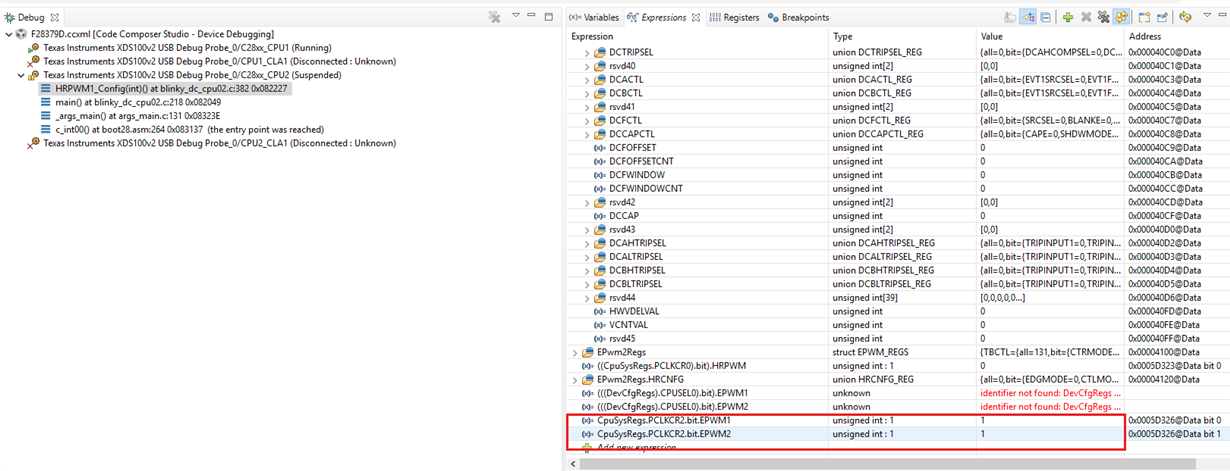

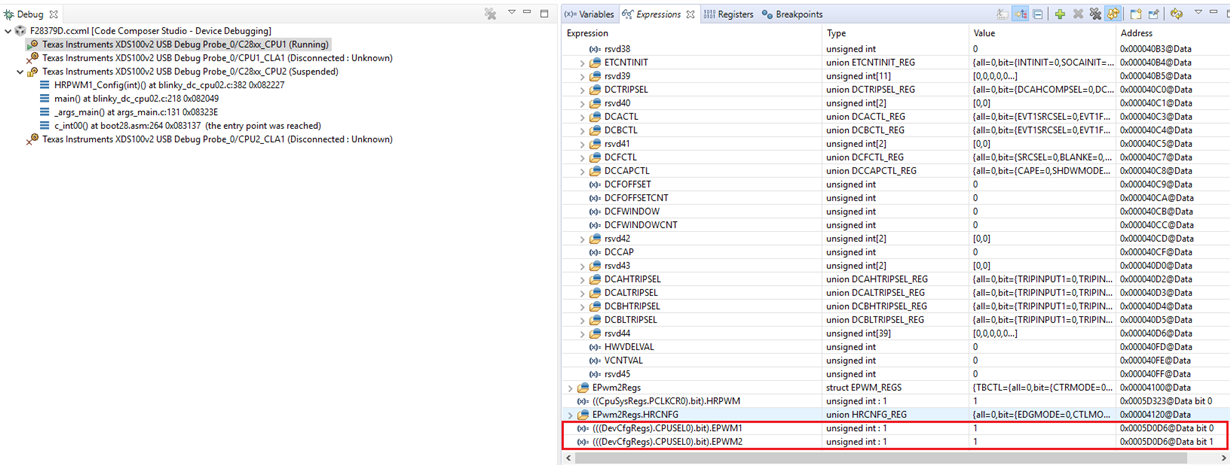

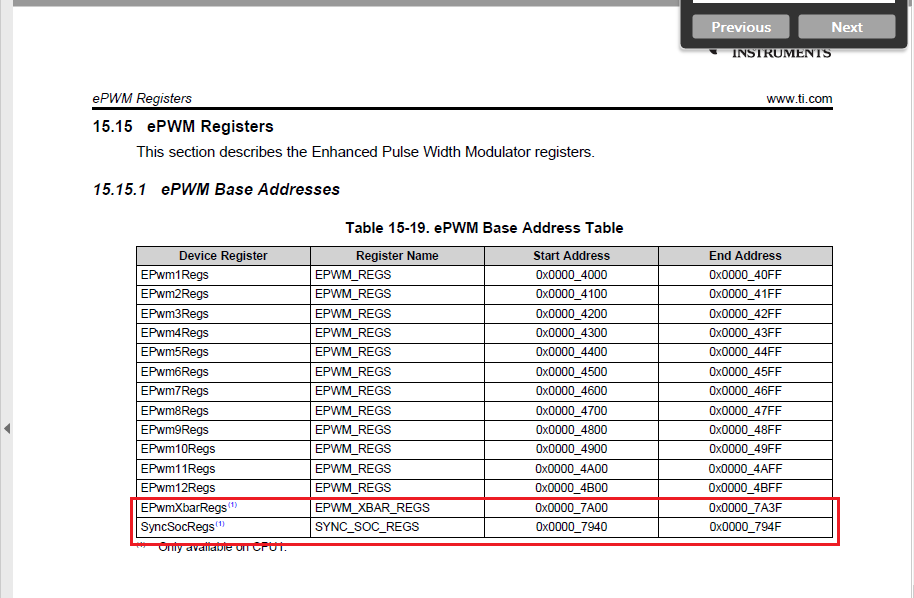

But when I check all the registers of ePWM1 and ePWM2 I see the values are set correctly except for HRCNFG register. I am not sure why this is happening. This issue is not present in CPU1 as I am able to run the example code properly in CPU1. And this issue affects only HRCNFG register and does not impact any other register settings.

I have attached screenshots from CCS with break point set to the particular instruction which will update HRCNFG register value for ePWM1, after executing the instruction by stepping over the code I still cannot observe the value in debug window but if I step through the next instruction which will set HRPE value in HRPCTL register it is updated properly.

I have also ensured that the ePWM1 and ePWM2 are allocated properly to CPU2 and clock is enabled for both ePWM1 and ePWM2.

I have also attached the source code which I have used for both CPU1 and CPU2.

CPU1

CPU2

Please let me know how to solve this problem.

Thanks,

Aditya