Part Number: TMS320F28374D

Other Parts Discussed in Thread: TMS320F2837,

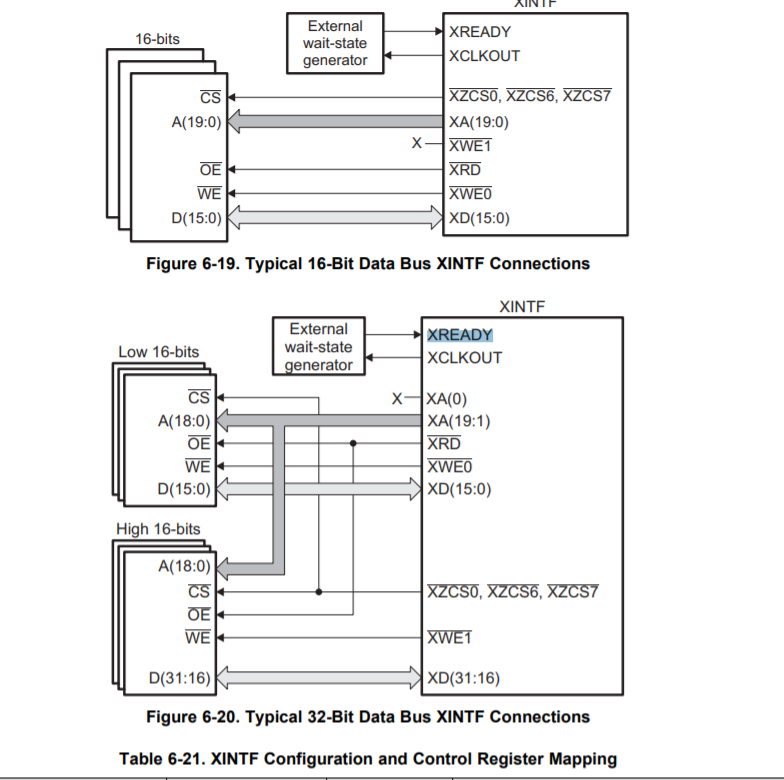

We are developping a new board with TMS320F28374D, the DSP is connect to Asyncronous RAM and to a FPGA using External Memeory interface bus. In the old board we have the DSP TMS320C2834x the XINF interface requires the XREADY and XCLOCKOUT signals. For TMS320F2837 these signals are not present, is it right? Can we omit them?