Other Parts Discussed in Thread: C2000WARE

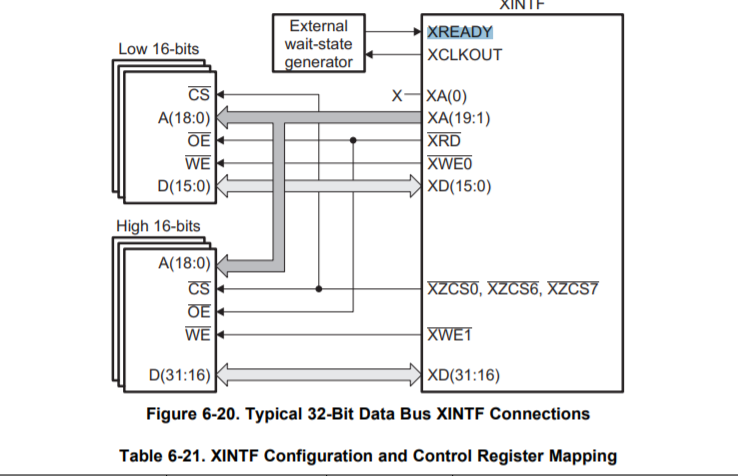

In our old board with DSP TMS320C2834 we have a configuration of external memory interface like the figure

In the second chip we use XWE1 signal connect to WE pin of the RAM.

Is There a signal like this in DSP TMS320F28374D? it is possible to have tow different WE using a 32bit data bus?