Part Number: TMS320F28377S

Other Parts Discussed in Thread: CONTROLSUITE, C2000WARE, UNIFLASH

Hi,

I followed the instructions in this document to flash my micro through SCI and it seemed to work properly until I got to the last bit and I was not prompted with the operation I wanted to perform (DFU in my case).

This is what is listed in the reference manual:

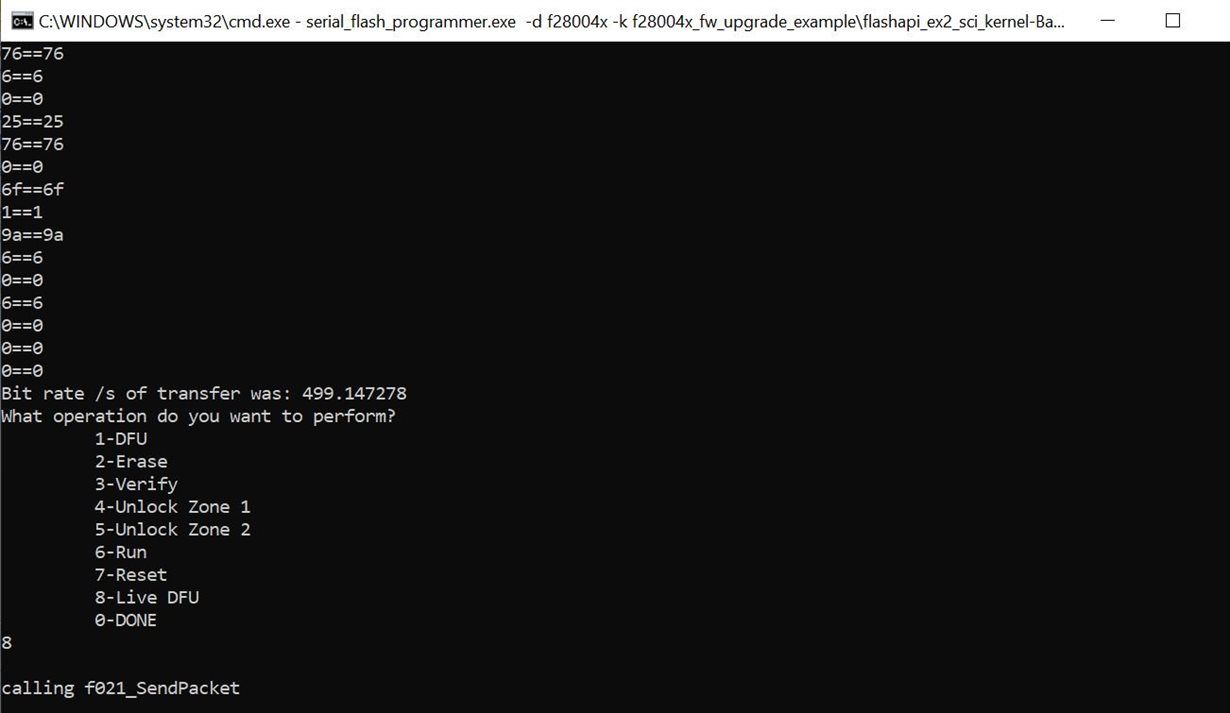

And this is what Mine looks like:

I have tried waiting but nothing ever pops up after this. How can I get the prompt I need to run the DFU?

Thank you for your help,

Trevor