Part Number: TMS320F28075

Hi Expert,

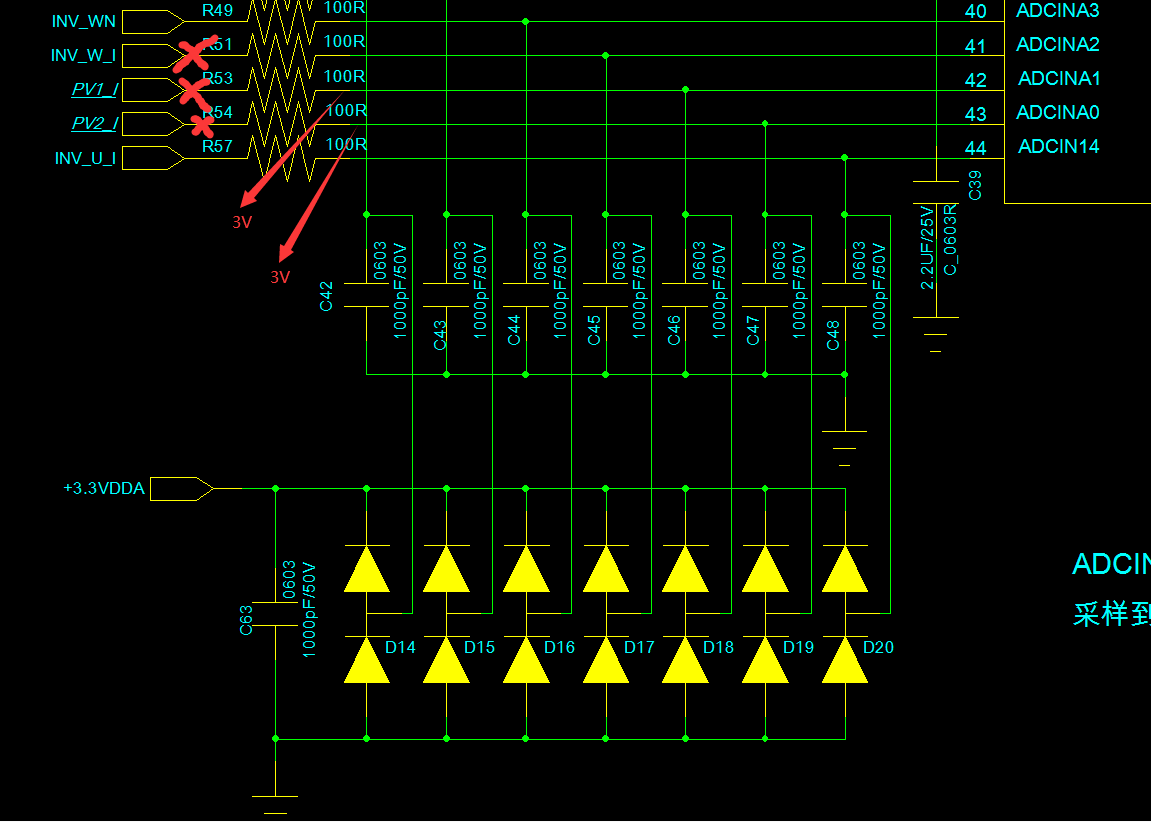

As the figure1 shown, remove R51, R53, R54 resisters from ADCINA2/1/0 pins, and connect 3V voltage with ADCINA0 & ADCINA1.

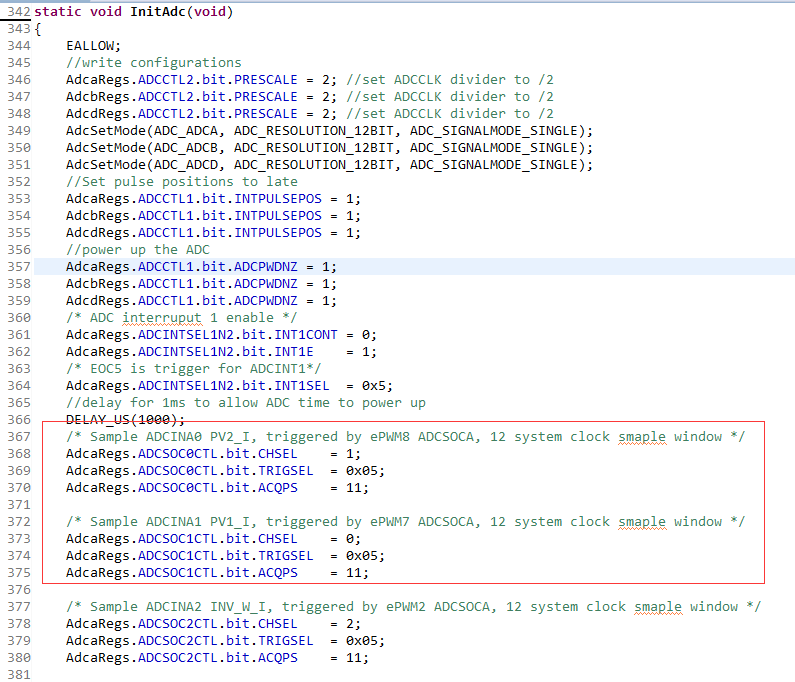

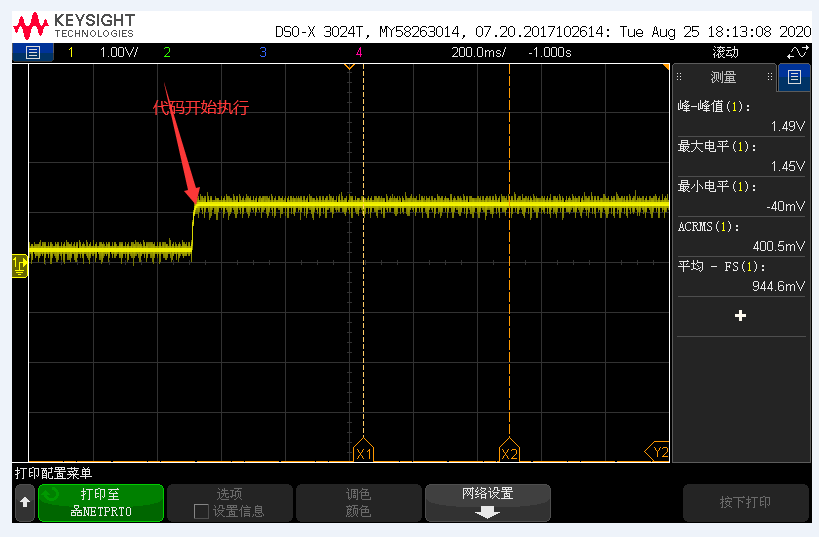

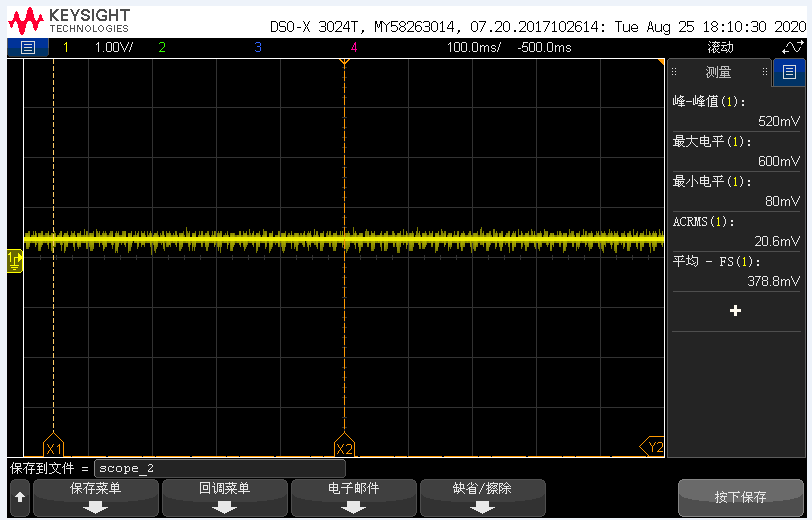

- There's a step change of ADCINA2 input signal as figure3, when the software is executed, configured as figure2, which SOC0 sampling ADCINA1, SOC1 sampling ADCINA0.

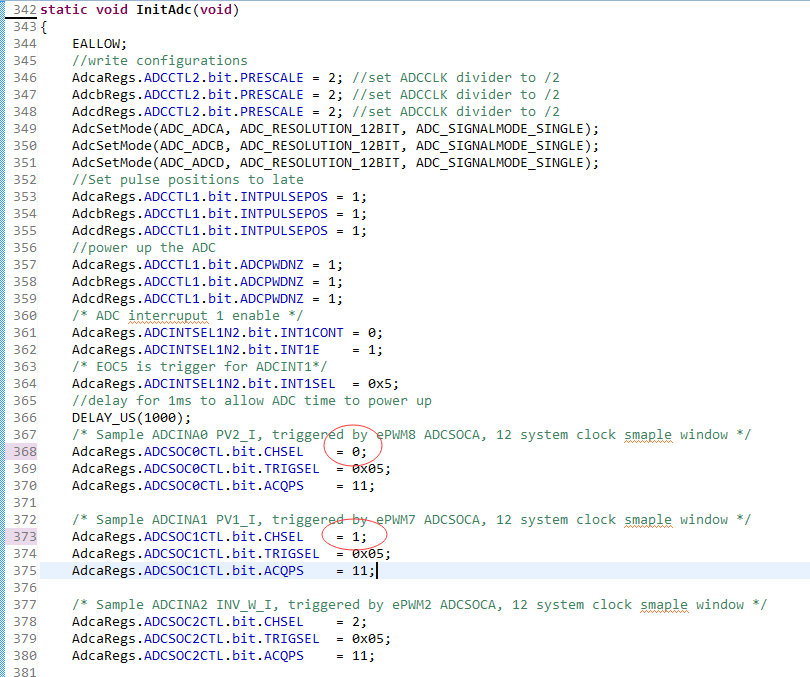

- However, there's normal low level voltage of ADCINA2 as figure5, if change the software that SOC0 sampling ADCINA0, SOC1 sampling ADCINA1.

From the test result, the ADCINA2 signal is influenced by ADCINA0/1 sampling sequence.

Could you please help to explain why this happens and how to avoid this issue? Thanks!

Figure1 hardware schematic diagram

Figure2 ADC software configuration with SOC0-> ADCINA1

Figure3 ADCINA2 input signal with SOC0-> ADCINA1

Figure4 ADC software configuration with SOC0-> ADCINA0

Figure5 ADCINA2 input signal with SOC0-> ADCINA0

Best Regards

Rayna