Hi Experts,

A customer configured that ePWM1 is the master and ePWM2 to 6 are the slave.

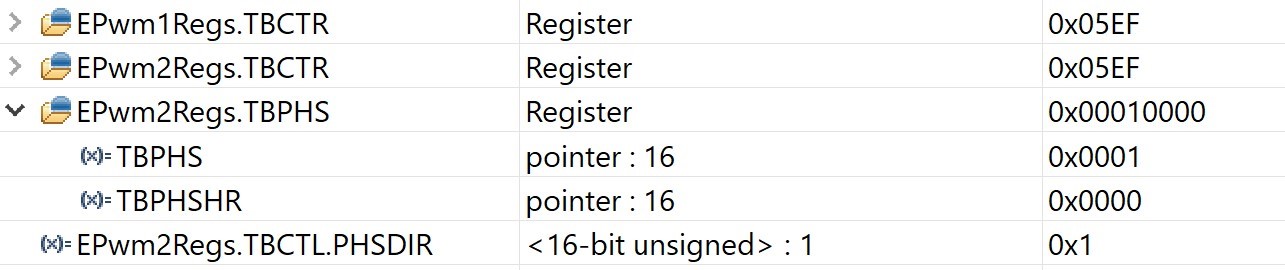

And then the TBCNTs for each ePWM was captured and there confirmed 2 clocks differences between the master and the slaves.

When TBPHS=2 was set to the ePWM2 to 6 which are slaves, 4 clock differences confirmed.

I believe that TBCNTs for ePWMs are synchronized if TBPSH=2 for the salves.

So could you please check the correct method and let me know what I should check their settings.

Thank you for your kind support.

Best regards,TI_F280049_ePWM1to6_Sync_TBCNT.pdf

Hitoshi