Tool/software: Code Composer Studio

Hi, there.

I met a problem when executing code ReadMultiBytesWithStartAddr() like the attached one :I2C_ReadTest.zip

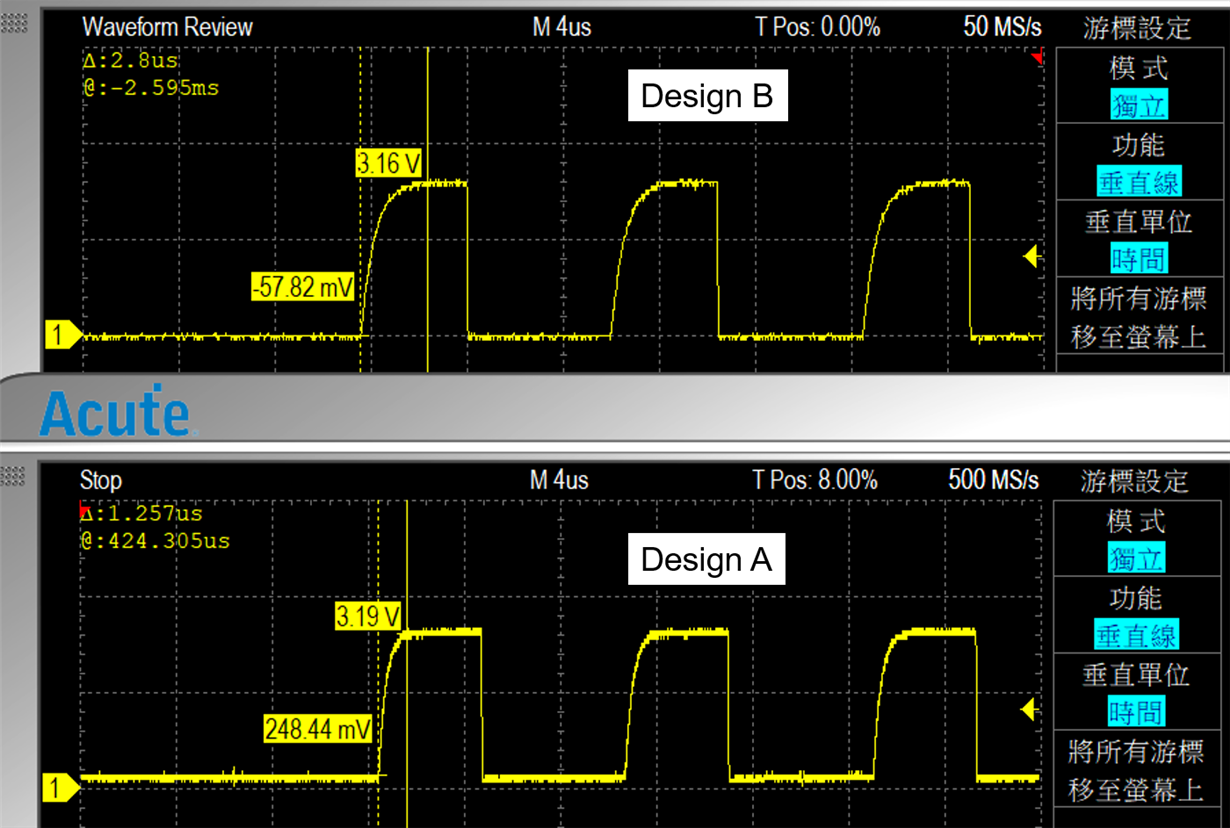

Sometimes it just worked fine, but sometimes it received data and put a "NACK". After logic analysis, it is inspected that some byte seems to "lack a clock pulse" probably as shown below :

In normal situation, you will see like :

When it works abnormally, you will see like :

Why's that? Did you have any suggestion?

Thanks.