Part Number: TMS320F28379D

Other Parts Discussed in Thread: LAUNCHXL-F28379D, C2000WARE,

Hi community!

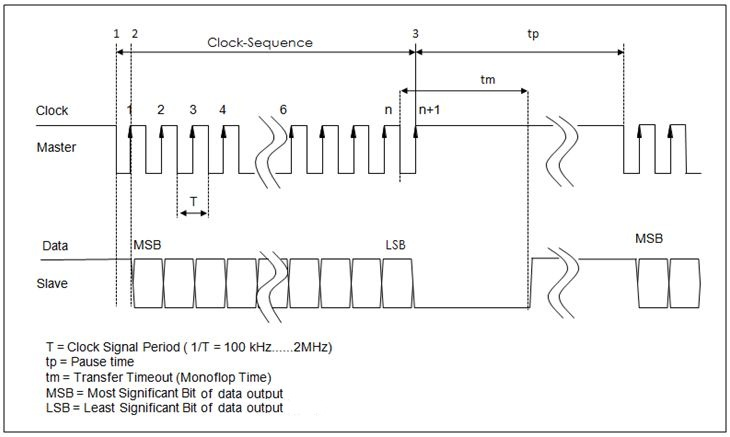

I am using a LAUNCHXL-F28379D for the communication with a SSI absolute encoder. According to the datasheet of the encoder, I need a constant time delay (tm) between the clock cycles. Besides, the number of bits that should be received in each cycle is 13.

For generating the mentioned delay, I have configured the SPI module in FIFO mode. I tied to provide the delay by using SPIFFCT. However, based on the delay of the code execration, the delay varies! here you can find my code:

for(;;)

{

sdata = 56;

sdata = sdata*8;

// Transmit data

spi_xmit(sdata);

// Wait until data is received

while(SpiaRegs.SPIFFRX.bit.RXFFST !=1) { }

// Check against sent data

delay_loop();

rdata = SpiaRegs.SPIRXBUF;

// if(rdata != sdata) error();

}

It sends a number (e.g. 56) and recives it back in "rdata". However, changing the "delay_loop()" length, changes the delay that has been set by SPIFFCT. Here are my configurations:

void spi_init()

{

SpiaRegs.SPICCR.all =0x004C; // Reset on, rising edge, 16-bit char bits

SpiaRegs.SPICTL.all =0x0006; // Enable master mode, normal phase,

// enable talk, and SPI int disabled.

SpiaRegs.SPIBRR.all =0x0031;

SpiaRegs.SPICCR.all =0x00DC; // Relinquish SPI from Reset

SpiaRegs.SPIPRI.bit.FREE = 1; // Set so breakpoints don't disturb xmission

}

void spi_xmit(Uint16 a)

{

SpiaRegs.SPITXBUF=a;

}

void spi_fifo_init()

{

// Initialize SPI FIFO registers

SpiaRegs.SPIFFTX.all=0xE040;

SpiaRegs.SPIFFRX.all=0x205F;

SpiaRegs.SPIFFCT.all=0x7;

}

Would anyone please help me? Is there any better way for providing the constant delay as written in the datasheet? (about 12 us).

Regards.