Hello,

I am using F28388D for our project.

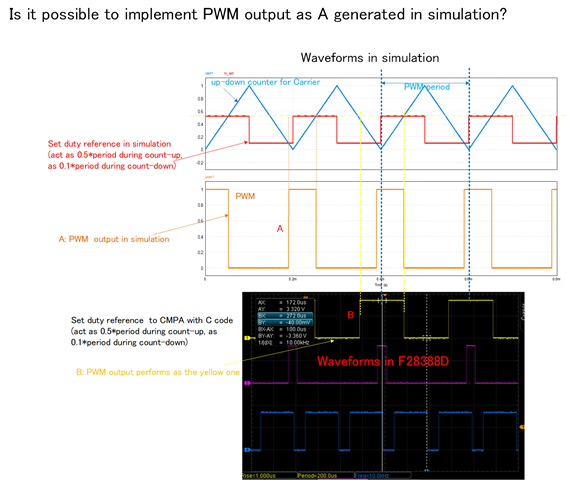

Is it possible to reload PWM output twice with two new values wrote in CMPA during one PWM period.

I tried to implement this, unfortunately, the result shows PWM output only reloaded once in a PWM period.

Since my count mode is configured as up-down, one PWM period means: one PWM period = 2 x TBPRD × TTBCLK.

Here is my experiment environment:

- Up-down count mode

{EPwm1Regs.TBCTL.bit.CTRMODE = 2U;}

- Enable PWM interrupt event: time-base counter equal to zero or period (TBCTR= 0x00 or TBCTR = TBPRD).

{EPwm1Regs.ETSEL.bit.INTSEL = 3U;}

- Active Counter-Compare A (CMPA) Load From Shadow Select Mode Load: on either CTR = Zero or CTR = PRD

{EPwm1Regs.CMPCTL.bit.LOADAMODE =2U;}

- Set duty reference to CMPA, which acts as 0.5*period during count-up, as 0.1*period during count-down in PWM interrupt

{status = EPwm1Regs.TBSTS.bit.CTRDIR;

if (1U==status)

{m_set = 0.1F;}

else if (0U==status)

{mu = 0.5F;}

else{}

}

Please find the attached PWM waveforms and a simulation result with twice reloaded PWM for your comparison.