Part Number: MSP430F67671A

Hello

I refer to the following files.

SLAU208Q (MSP430x5xx and MSP430x6xx Family User's Guide)

SLAS983A (MSP430F677x1A Data sheet)

SLAS655G (MSP430F543xA Data sheet)

1. ADC10_A

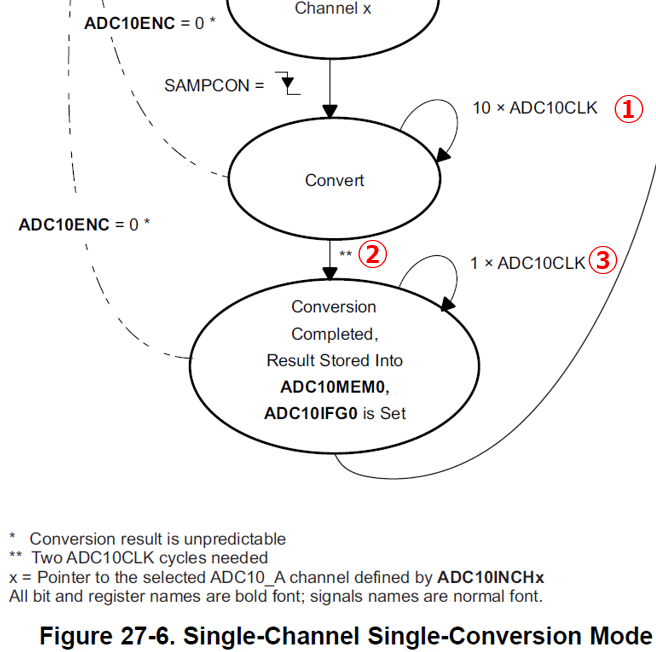

Figure 27-3 (SLAU208Q)

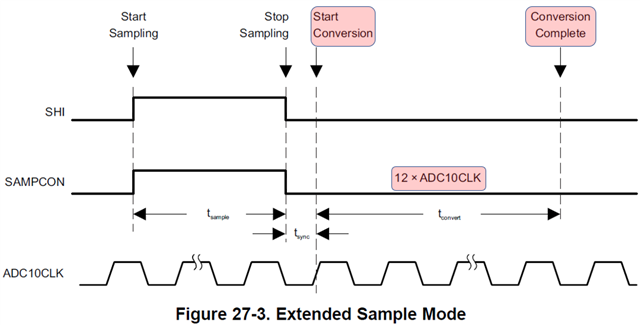

Table 5-48 (SLAS983A)

It seems that the conversion time is 12clk of ADC10CLK.

On the other hand,

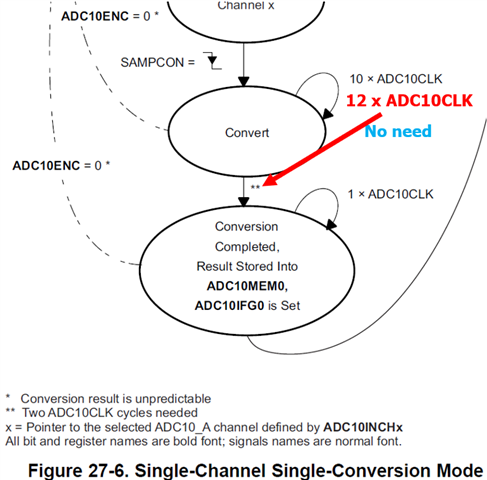

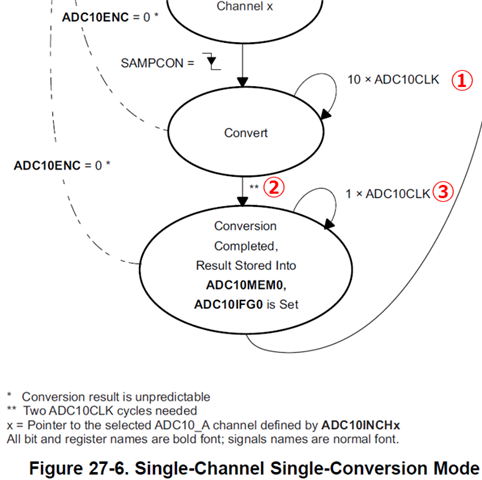

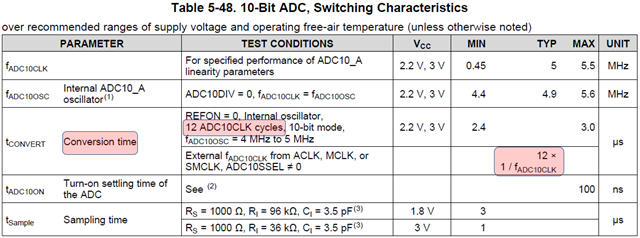

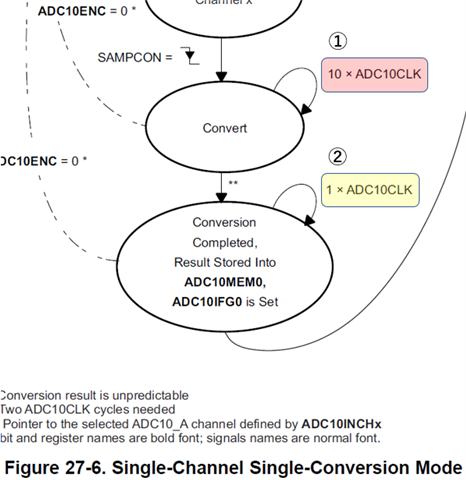

Figure 27-6 (SLAU208Q)

①:Convert : 10 x ADC10CLK

②:Result Stored Into ADC10MEM0, ADC10IFG0 is Set : 1 x ADC10CLK

Q1.

Is not ① 12 x ADC10CLK ?

2. ADC12_A

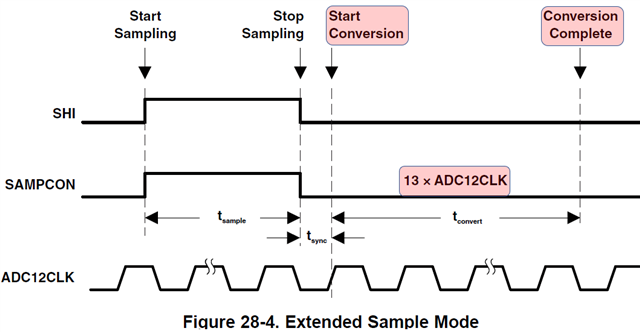

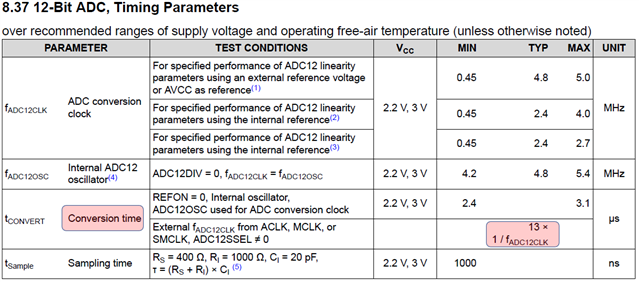

Figure 28-4 (SLAU208Q)

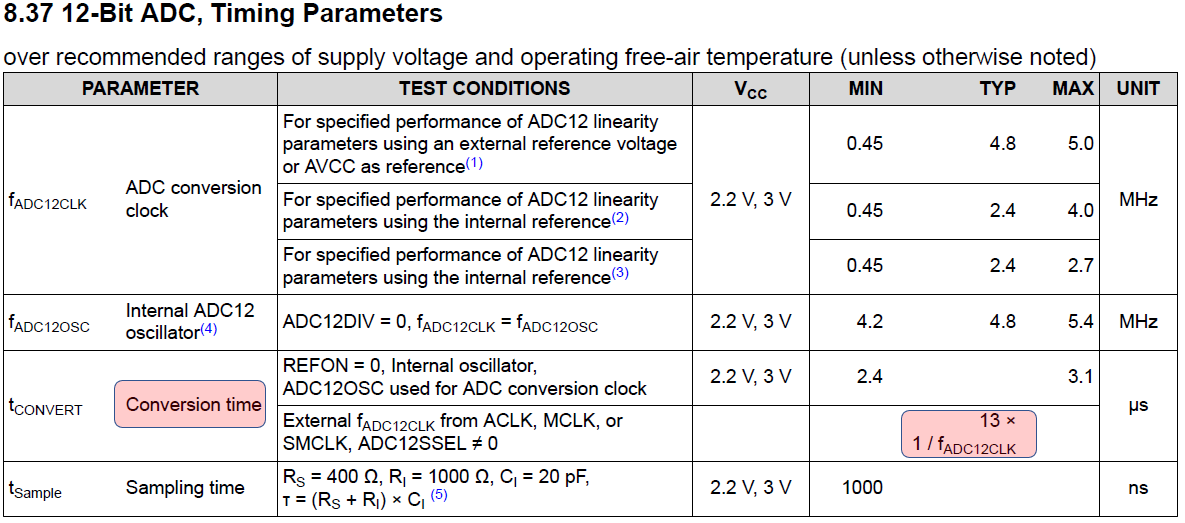

8.37 12-Bit ADC, Timing Parameters (SLAS655G)

It seems that the conversion time is 13clk of ADC12CLK.

On the other hand,

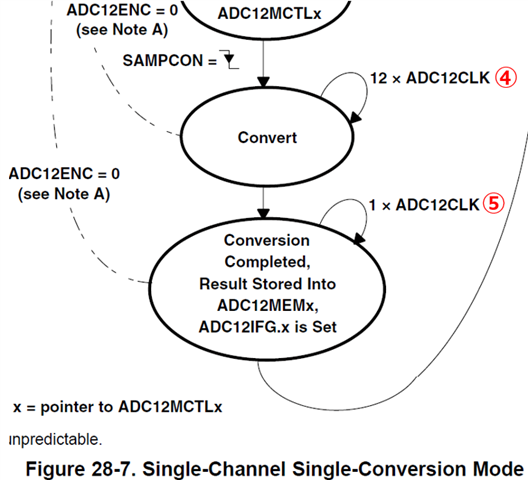

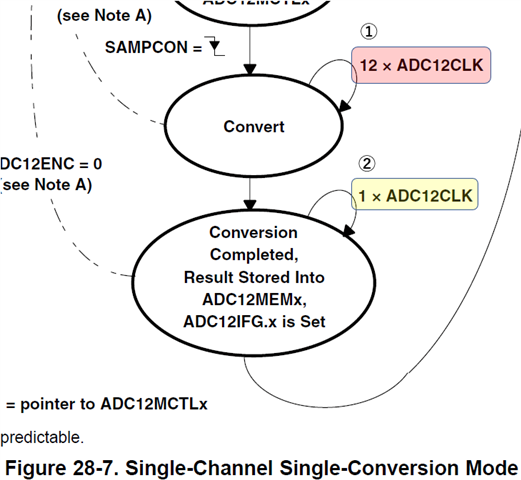

Figure 28-7 (SLAU208Q)

①:Convert : 12 x ADC12CLK

②:Result Stored Into ADC12MEMx, ADC12IFGx is Set : 1 x ADC12CLK

Q2.

Is not ① 13 x ADC12CLK ?

Best Regards,