Other Parts Discussed in Thread: MSP430WARE

I'm using the driverlib SDK Timer_A_outputPWM() function to generate a PWM signal on TA0.1. A PWM signal is produced with the correct duty cycle, but the period is twice what I expect it to be.

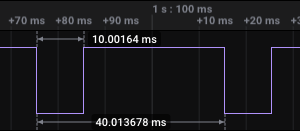

By my calculations, the period should be 20ms, but the period of the generated waveform is 40ms. SMCLK is running at about 2 MHz. I have verified this using CS_getSMCLK(). I'm dividing the clock signal by 40 down to 50 KHz. 1000 / 50 KHz should be 20ms, or am I missing something?

GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P1, GPIO_PIN1, GPIO_SECONDARY_MODULE_FUNCTION); Timer_A_outputPWMParam TimerParams; TimerParams.clockSource = TIMER_A_CLOCKSOURCE_SMCLK; TimerParams.clockSourceDivider = TIMER_A_CLOCKSOURCE_DIVIDER_40; TimerParams.timerPeriod = 1000 - 1; TimerParams.compareRegister = TIMER_A_CAPTURECOMPARE_REGISTER_1; TimerParams.compareOutputMode = TIMER_A_OUTPUTMODE_RESET_SET; TimerParams.dutyCycle = 750; Timer_A_outputPWM(TA0_BASE, &TimerParams);