Other Parts Discussed in Thread: ADS1261

Dear Sirs

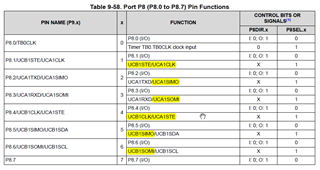

I will be using the SPI interface for my communications. The MSP430F5335 list four SPI channels, USCIA0, A1, B0 and B1. USCIA0 and B0 are available on P2 by port remapping and USCIA1 and B1 on P8. However, it seems that I can use only A or B on each port but not both due to clock/chip select conflicts between A and B, (please see below). Am I correct in this assumption? In addition, is the STE (slave transmit enable) the same as the CS sent from the master to the slave to enable the slave? Thank you for your time.