Hi,

I have a question in the continuation of the E2E thread below.

[Question1]

MSP430x2xx Family User's Guide (Rev. J) --2.2.1.1 Reset / NMI Pin has the following text.

------

If the RST / NMI pin is set to the reset function, the CPU is held in the reset state as long as the RST / NMI pin is held low. After the input changes to a high state, the CPU starts program execution at the word address stored in the reset vector, 0FFFEh, and the RSTIFG flag is set.

----------

From this sentence, I think that the CPU cannot start the program when the High signal (it has not been set to the Low signal in advance) is input to the RESET terminal.

Is this perception wrong? Also, please tell me the behavior of the MCU at this time. (The MCU operates uncertainty. Memory corruption may occur, etc.)

[Question2]

A reset IC is connected to the RST pin, and the reset duration is 7 ms. In this case, can the reset operation and the BOR operation interfere with each other? Is there any uncertainty operation such as memory corruption?

Since either reset or BOR works, I don't think it will interfere.

[Question3]

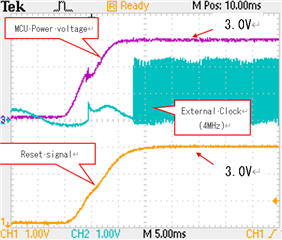

If the voltage of the reset terminal is High when the power is applied to the MCU, may the DCO and watchdog not start?

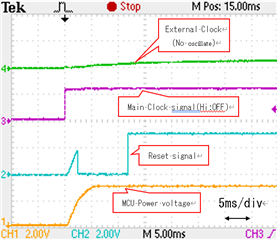

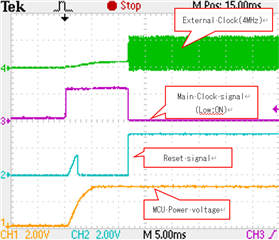

This is for the case where the voltage of the reset terminal is High when the power is applied to the MCU. After that, the external clock oscillates after the reset input voltage changes from Low to High.

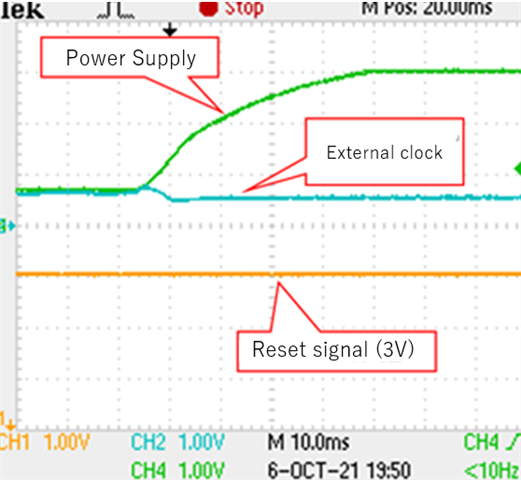

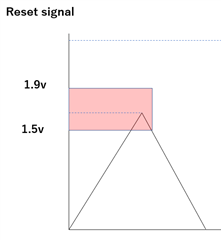

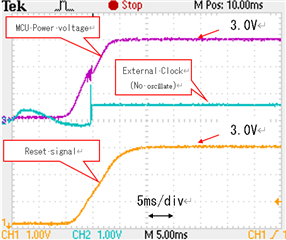

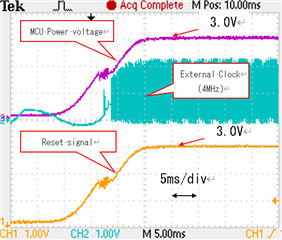

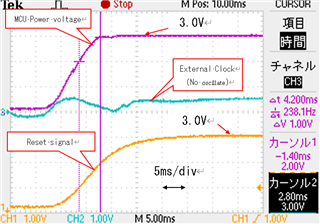

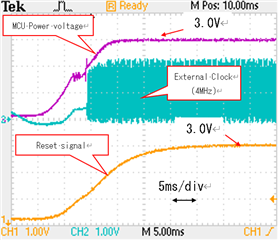

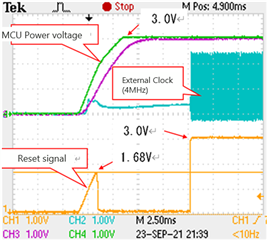

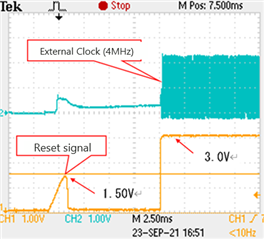

As shown in the figure below, when the reset voltage is 1.7V or less when the microcomputer is started, the external clock oscillates and the microcomputer operates.

It may not oscillate.

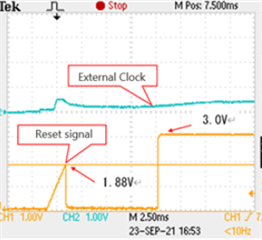

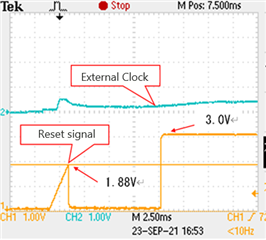

In this case, the reset input voltage when starting the MCU is 1.88V.

We are very sorry, but we would like an answer as soon as possible.

Best regards,

Koki