Hi team,

Here's an issue from the customer may need your help:

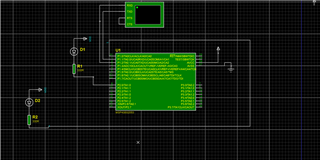

When simulating the serial UART of the msp430G2553 using the proteus8.6, the PI ports are all low, and the following diagram shows the schematic of the simulation:

And the code is as follows:

#include <msp430.h>

/**

* main.c

*/

#define uchar unsigned char

#define CPU_CLOCK 1000000

#define delay_us(us) __delay_cycles(CPU_CLOCK/1000000*(us))

#define delay_ms(ms) __delay_cycles(CPU_CLOCK/1000*(ms))

void SendData(uchar Data)

{

UCA0TXBUF = Data;

delay_ms(1000);

P1OUT &= 0XFE;

// TX -> RXed character

while (!(IFG2&UCA0TXIFG)); // USCI_A0 TX buffer ready?

if ((IFG2&UCA0TXIFG));

{

P2OUT = UCA0TXBUF ;

}

delay_ms(1000);

}

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // stop watchdog timer

DCOCTL = CALDCO_1MHZ;

BCSCTL1 = CALBC1_1MHZ;

P2DIR |= BIT0;

P1DIR |= BIT0;

BCSCTL2 = 0;//SMCLK is clocked from DCOCTL and divided by 1

//Reset USCI_AX

UCA0CTL1 |= UCSWRST;

UCA0CTL0 =0;//USIC select USART

UCA0CTL1 = UCSSEL1+(UCSWRST); //configure usic clock as SMCLK

UCA0BR0 = 104;

UCA0BR1 = 0x00;

UCA0MCTL = 0X02;

//enable IO port

P1SEL |= 0x06 ;

P1SEL2 |= 0x06;

UCA0CTL1 &= (~UCSWRST);

IE2 |= UCA0RXIE;

while(1)

{

P2OUT = 1 ;

P1OUT |= BIT0;

SendData(0x00);

delay_ms(1000);

}

Please see the link below:

https://e2echina.ti.com/cfs-file/__key/communityserver-discussions-components-files/55/ppp.zip

Could you help check this case? Thanks.

Best Regards,

Cherry