Hi,

I have a question from my customer.

Suppose ACLK source is XT1 LF (the default condition) and WDT-A is sourced from ACLK.

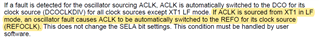

At device power-up, XT1 LF is not stabilized, so ACLK is automatically switched to REFOCLK, according to user's manual section 5.2.12 "UCS Module Fail-Safe Operation".

On the other hand, section 16.2.5 Clock Fail-Safe Feature in WDT-A says:

As ACLK is maintained thanks to the UCS fail-safe, I guess the fail-safe feature in WDT-A is not triggered at power-up.

So WDT-A is sourced from ACLK (REFOCLK) not VLOCLK.

Correct?

Thanks and regards,

Koichiro Tashiro

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.