I am using the msp430's timer output to generate a PWM. I need the full scale from 0 to 100 % duty cycle.

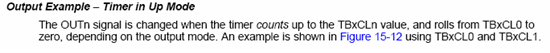

The timer is setup in Continuous mode (it is used for other stuff as well). The output modes used for generating PWM use the EQU0 and EQUx interrupt events for switching the output signal.

For example in output mode 7 (Reset/Set), the signal gets low on EQUx event, and high on EQU0 event.

Is there any description of what happens if TACCR0 is equal to TACCRx? As far as I can see the behavior is not specified. Maybe there is a hierarchy of the EQU events, that I missed?

I can test and see what the chip actually does, that is not the problem. What I want to know is if the situation is specified somewhere, or if I have no right to expect anything.

If this is unspecified, my solution is to use the Set and Reset modes in the relevant cases.

Even if specified, TACCR0 == TACCRx means either 0 % or 100 %, and I need to take care of the other case with Set or Reset mode (or Output mode).

I suspect that I am not the first one to wonder, is there a common practice for this full-range PWM application?