Other Parts Discussed in Thread: UNIFLASH, MSP-FET, , MSP430FR5994

Hello,

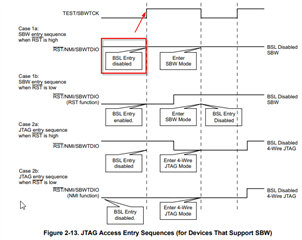

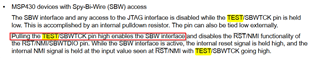

We are having a problem with the CryptoBSL entry sequence not consistently functioning.

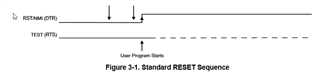

1) Standard Reset -- fails to reset MCU, 12us duration on RST

Note: the time between resets was varied by 1 - 5 seconds

2) Standard Reset -- fails to reset MCU, 12us duration on RST

3) CryptoBSL Entry Sequence -- fails after polling 0x48 for 50ms (ACK failure)

4) Standard Reset -- success, 12us duration on RST

5) Standard Reset -- fails to reset MCU, 12us duration on RST

6) Standard Reset -- fails to reset MCU, 12us duration on RST

7) CryptoBSL Entry Sequence -- success after polling 0x48 for 10ms

8) Standard Reset -- success, 12us duration on RST

9) Go to step 1

1) Standard Reset -- success, 12us duration on RST 2) Standard Reset -- success, 12us duration on RST 3) CryptoBSL Entry Sequence -- success after polling 0x48 for 10ms 4) Standard Reset -- success, 12us duration on RST 5) Go to step 1

Thank you so much in advance for you help with this!