Hi all!

I aim to set MCLK to 8MHz. While debugging in CCS, I get strange output on PJ.1. Once I click "terminate" to stop the debug, the clock looks perfect on the oscope. Any idea why this is?

I am outputting MCLK to PJ.1:

PJSEL |= BIT0 + BIT1 + BIT2; //Output CLKs to PJ.0-2 PJDIR |= BIT0 + BIT1 + BIT2;

I aim for a 8MHz MCLK speed:

// configure clocks

UCSCTL3 = SELREF_2; // Set DCO FLL reference = REFO

UCSCTL4 |= SELA_2; // Set ACLK = REFO

__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0 = 0x0000; // Set lowest possible DCOx, MODx

UCSCTL1 = DCORSEL_5; // Select DCO range 16MHz operation

UCSCTL2 = FLLD_1 + 243; // Set DCO Multiplier for 8MHz

// (N + 1) * FLLRef = Fdco

// (243 + 1) * 32768 = 8MHz

__bic_SR_register(SCG0); // re-enable the FLL control loop

// Worst-case settling time for the DCO when the DCO range bits have been

// changed is n x 32 x 32 x f_MCLK / f_FLL_reference. See UCS chapter in 5xx

// UG for optimization.

// 32 x 32 x 8 MHz / 32,768 Hz = 250000 = MCLK cycles for DCO to settle

__delay_cycles(250000);

// Loop until XT1 & DCO stabilizes - In this case only DCO has to stabilize

do

{

UCSCTL7 &= ~(XT1LFOFFG + XT1HFOFFG + DCOFFG);

// Clear XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

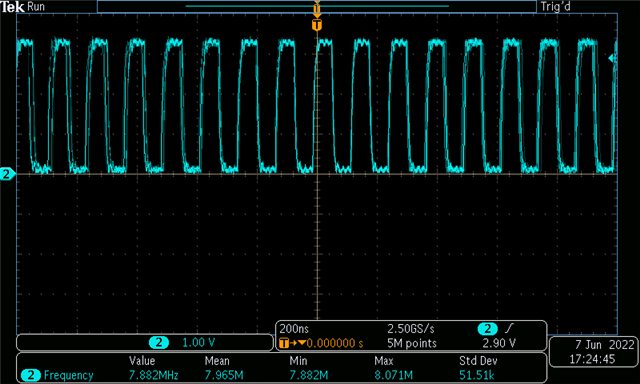

When using CCS Debugger, my oscope shows a strange clock signal:

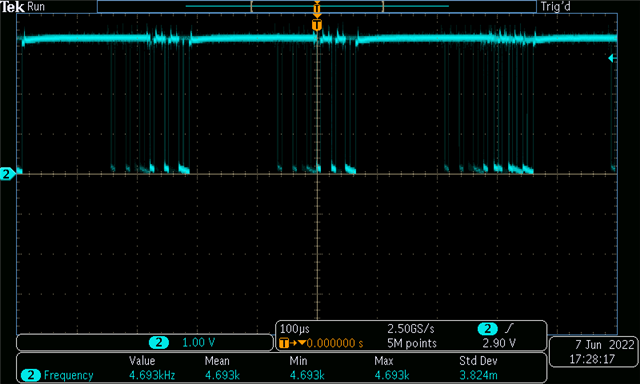

However, when I click "terminate", my oscope shows a clean MCLK exactly what I hope for: