Part Number: MSP430FR2675

Hi,

I am working on fixing an issue that we are seeing in manufacturing and believe I have found a bug in the driver library for the MSP430FE2xx_4xx parts; version: 2.91.13.01.

We are seeing an issue when we set the clock up with CS_initFLLCalculateTrim(3000, 3000/34, stuct). The 34 was previously 32 and this worked with our prototypes, when we got to production we saw some issues with some parts not getting through the clock init and based on feedback from a TI FAE(I can't find the emails), we changed to 34 and that worked for awhile and now we are seeing the same issue.

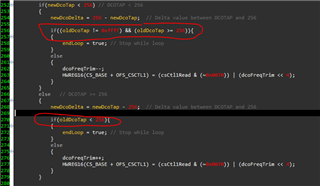

I can get it working again if I increase the divider from 34 to 35 but while troubleshooting, I realized that the loop in the CS_initFLLCalculateTrim appears to track the best setup but will loop continuously until it is inside the values set if it isn't within the defined range.

I was hoping to talk with an FAE about this and see if there is a possible bug in the library or something.

Thanks,

Ryan