Hi team,

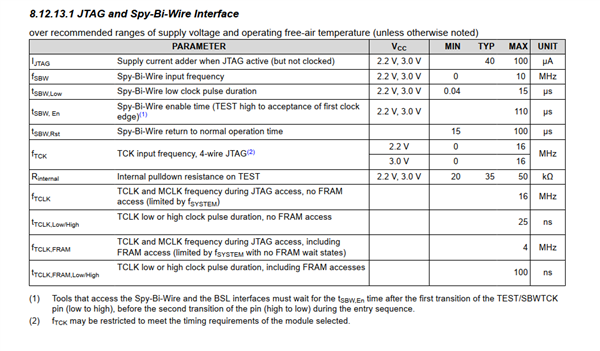

My customer want to confrim value of tSBW, en, at User's Guide "MSP430 FRAM Devices Bootloader (BSL) ", section 8.12.13.1 JTAG and Spy-Bi-Wire Interface, TSBW, en defined max= 100us only.

Based on this, customer tested wirting with BSL entry sequence (Figure 3-2), but it is not possible when the value is set to 55us. So then changed to 165us, can write eventually.

From the result of fact, TSBW, en must be set over 110us?