This is ongoing over multiple board revs and designers over the years. It's showtime for a new product, it's one of the last items, so appreciate any help here. Thanks in advance!

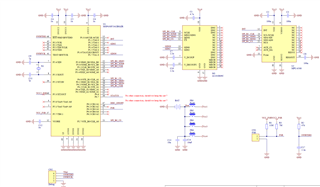

Before getting into the circuits etc, my coder and I have inserted this to address the hidden P7 and P8 pins per errata. Is this correct and sufficient? (Let me know if you need to see the errata and I'll find it, but also looking for general info like if other port settings are also needed below for P7 & P8).

/* Enable pull resistors of port 7 & 8 pins to save power */

uint16_t * pu16_p78ren_reg = (uint16_t *)0x0266;

*pu16_p78ren_reg = 0x07FF;

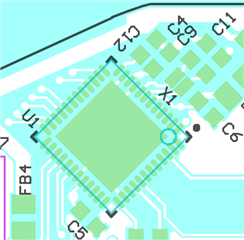

Next, at a high level, the symptoms are that sometimes it will sleep at a nice 27uA. Other times it will go there for a split second, then ramp up to anywhere up to about 1 ma. Almost like a floating port. All unused are output low before sleeping. System uses the internal ADC12, SPI talking to a Motion and RF module (which are not leaking but connected still).

Additionally, I'm using a low solids flux and tin/lead for prototypes. I seem to be able to get it to stay at 27uA with a good IPA cleaning, soap, you name it I've tried it. Ultrasonic cleaning is not recommended due to the inertial sensor, but that didn't resolve either. This cleaning part seems like the wrong tree, nothing should be that sensitive right?

Next I've considered ESD damage. So how sensitive are these ports and does a blown port behave this way from static? I have noticed on some I can bring my hand (capacitance) near the chip and it will go back down to 27uA. (I think it's watching me and laughing!). Sounds float related right?

FYI, we have this chip wirelessly updating firmware on sub gig through our own dongle and App, so it's come along way as a Realtime foot controller. But that also means it's complex and we'll need to pick and choose code sections as they relate. I have over 500 of these processors on hand so hope we can make them work.