Hi everyone,

Using MSP430F67751A series microcontroller for a long time in a mass production. But in some products we started to see specific DMA transfer problems.

We use a algorithm where "Timer1 A1 Interrupt" triggers autoscan for 10 bit ADC channel which Autoscans 4 different channel and after that triggers DMA action. The problem is we started to see "0" values in our readings in some products. Adding a conditional statements for ADC operation ,where we neglect "0" values, ended up with missing datas in UART and I2C channels. In UART peripheral we using polling method if it may helpful to know. Also we experience this situation, if we start to use "Timer3 A1 Interrupt" which is a critical point at our software where we start to increase processer load at the parallel.

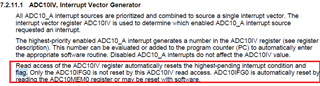

Examining ERRATA (see: https://www.ti.com/lit/er/slaz590v/slaz590v.pdf) for specific DMA problems we came accross a specific problem stated with "DMA7" code. Errata says DMA transfers may cause loss of interrupts. But why it is not happening in our all products. Since we call ADC scan at the end of "Timer1 A1 Interrupt" how DMA action may cause loss of interrupt if we not read or write to that specific peripheral. Also how it is possible to all success flags for DMA and ADC peripherals are setted while reading is completely false. We also examined input signal with oscilloscope and have seen no spike nor cut at it.

Thank you, kind regards.