Other Parts Discussed in Thread: CCSTUDIO

Hi,

I am using an MSP430F5172 to create an interleaved PWM on Timer D0 with CCR1 and CCR2. D0 is running in up/down mode and CCR1/2 are operating in compare mode toggle-reset and toggle-set respectively.

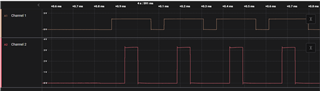

The PWMs are being staggered correctly; however, there is an issue on the first pulse when the timer kicks off where it has both outputs high at the same time, which is a scenario we are trying avoid.

Below is an image of the signals where D0.1 is TD0 CCR1 and D0.2 is TD0 CCR2.

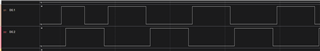

When analyzing these signals in TI's CCStudio example code tutorials, this phenomena also occurs. Is there a way around this? Is there a latent configuration issue?

TI's documentation states that this PWM setup is perfect for scenarios where both signals shouldn't be high at the same time, but this start-up behavior defeats the purpose... which makes me think I have a configuration issue.

Below is the setup code.

void init_timers(void)

{

struct s_TLV_Timer_D_Cal_Data * pTD0CAL; // Structure initialized in tlv.h

uint8_t bTD0CAL_bytes;

// Stop WDT

WDT_A_hold(WDT_A_BASE);

//Get TimerD0 Cal Values (instance 0)

TLV_getInfo(TLV_TAG_TIMER_D_CAL, 0, &bTD0CAL_bytes, (uint16_t **) &pTD0CAL);

if(bTD0CAL_bytes == 0x0)

{

// No TimerD free running cal data found

while(1); // Loop here

}

/*

* Configuration

*/

// Setup TD0

TD0CTL0 |= TDCLGRP_0 | CNTL_0 | TDSSEL_2 | MC__UPDOWN | ID_0 | TDCLR;

TD0CTL1 |= TDIDEX_0 | TDCLKM_1;

// Enable high resolution clock

TD0HCTL0 = TDHEN + TDHM_1;

TD0HCTL1 = pTD0CAL->TDH0CTL1_128;

// Configure CCR modes

TD0CCTL0 |= TIMER_D_OUTPUTMODE_OUTBITVALUE;

TD0CCTL1 |= TIMER_D_OUTPUTMODE_TOGGLE_RESET;

TD0CCTL2 |= TIMER_D_OUTPUTMODE_TOGGLE_SET;

// Configure latching compare thresholds

...

}

Thank you for any assistance.