Other Parts Discussed in Thread: SN74AVC4T774

Hello,

I'm implementing SBW-based flash programming on the MSP430F5438A. Our board has a level-shifter (SN74AVC4T774RSV) between the host and the MSP430.

This level shifter allows one-way signal travel only. I.e.TCK and TDIO (TEST and RESET) can go from host to MSP430, -or- from MSP430 to host, but not both directions at the same time. This direction is controlled via a separate GPIO pin on the host.

A couple questions -

1) Is it possible to program the device with "one way" signals from the host to the MSP430?

- Signal direction is Host [TCK,TDIO] ====>> MSP430[TCK,TDIO]

- I know the exact MSP430 variant and its parameters, so I don't need to identify it.

- I won't know if I have connected successfully, so I'll have to work out a retry scheme after programming pass/fail.

2) If (1) is not possible, could this scheme work?

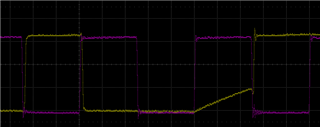

- Set things up, set/clear TCK as needed, switch signal direction to MSP430 --> host, read TDO, switch signal direction back to host --> MSP430, continue.

Thank you for your time.