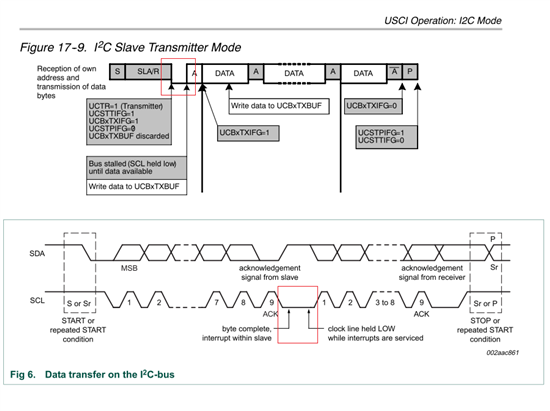

For msp430 series, the i2c clock stretching is implemented at the eighth falling edge.

However, referring to i2c specification 2.1/3.0, the i2c clock stretching is used at the nineth falling edge.

Will these differences cause i2c compatibility issues?