Guys –

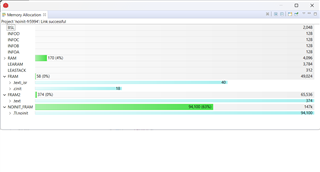

I am trying to use a msp430FR6007 in an application having two large arrays and three smaller ones. The large arrays are 63,000 bytes and 31,000 bytes. The smaller ones are a few hundred bytes each. The array must be nonvolatile and are located with the pragma NOINIT statement.

I had thought to locate them above 0x10000 although their location does not really matter. Nonvolatile NOINIT does matter, however.

I seem to be able to compile the program (a test version) but apparently cannot link it getting the errors “#10015-D output file cannot be loaded, etc.” and "#17003-D relocation from function "main" to symbol, etc.” for each array and variables associated with each array.

I have looked at the ti site and the forums but am not making progress. I think I do not understand how to set up the link command file and do not know how to achieve the result I desire.

How do I manipulate arrays such as I need to use and do so without violating address restrictions (I presume there must be some but I don’t know what they are!)? How do I set up the project and linker file to achieve my desired result?

Any help will be greatly appreciated. Are there any documents that would help? I've found and read the basic fram documents as well as several posts of the forum.

Regards

Bob Scott

214.673.1439

4/22/23