Part Number: MSP430F5510

Hi Team,

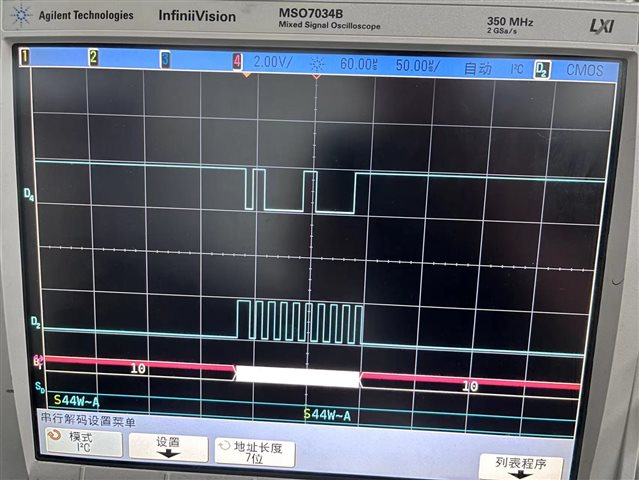

Customer is debugging I2C operation of msp430F5510+MAX7311 and is currently using code from routine, "MSP430F550x_uscib0_i2c_08.c". After the customer has configured the port, it now finds that the data cannot be sent after entering the interrupt and then exits from the interrupt. From the scope, it was stuck at the address where the Slave was sent, and then the SCL clock seemed to be having problems.

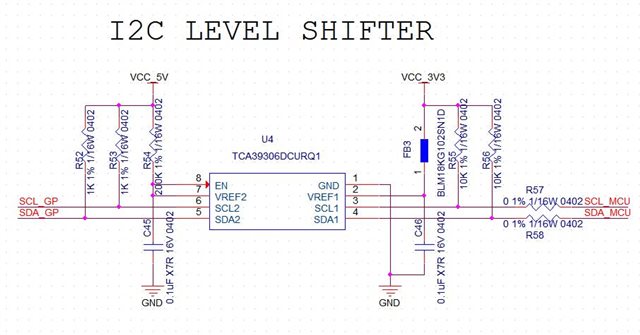

The schematic is as follows, the I2C of the monolithic is connected to a level-translation chip and a pull-up pin is connected to the I2C chip:

Once running to: UCB1CTL1 |= UCTR + UCTXSTT; // I2C TX, start condition

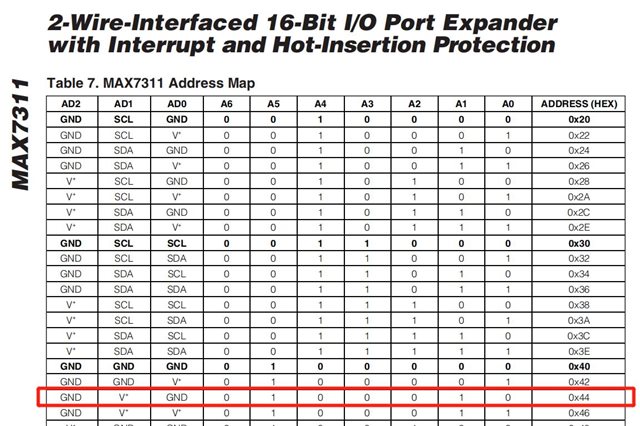

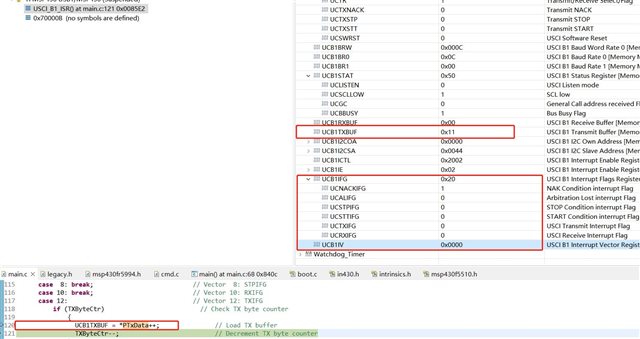

UCSCLLOW and UCBBUSY are set to 1, then an interrupt is entered, SCL is generated, and the slave address is sent (0x44 is set). Unable to continue sending slave_reg address and data afterwards.

Customer debug via break point and send data in UCB1I2CSA (0x44) with SCLK. The data in UCB1TXBUF (0x11) cannot be transmitted and the clock is missing (from the oscilloscope, the first eight bits of data and the ninth acknowledge bit are available. There should be no data or clocks starting at the 10th clock).

And the routine is here:

The code is as follows:

#include <msp430f5510.h>

#include "cmd.h"

#include <stdint.h>

#include <stdio.h>

unsigned char timeFlag;

unsigned char *PTxData; // Pointer to TX data

unsigned char TXByteCtr;

const unsigned char TxData[] = // Table of data to transmit

{

0x11,0x22,0x33,0x44,0x55

};

void writeI2C() {

PTxData = (unsigned char *)TxData; // TX array start address

// Place breakpoint here to see each

// transmit operation.

TXByteCtr = sizeof TxData; // Load TX byte counter

UCB1CTL1 |= UCTR + UCTXSTT; // I2C TX, start condition

__bis_SR_register(GIE);

__no_operation();

while (UCB1CTL1 & UCTXSTP); // Ensure stop condition got sent

}

void GPIO_Init(void)

{

PJDIR |= 0x01; // PJ.0 output

}

void I2C_Init(void)

{

P4SEL |= 0x06; // Assign I2C pins to UCB1 P4.1 P4.2

UCB1CTL1 |= UCSWRST; // Enable SW reset

UCB1CTL0 = UCMST + UCMODE_3 + UCSYNC; // I2C Master, synchronous mode

UCB1CTL1 = UCSSEL_2 + UCSWRST; // Use SMCLK, keep SW reset

UCB1BR0 = 12; // fSCL = SMCLK/12 = ~100kHz

UCB1BR1 = 0;

UCB1I2CSA = 0x44;

UCB1CTL1 &= ~UCSWRST; // Clear SW reset, resume operation

UCB1IE |= UCTXIE; // Enable TX interrupt

}

void timer0_Init(void)

{

TA0CCTL0 = CCIE; // CCR0 interrupt enabled

TA0CCR0 = 52616; // ~50ms

TA0CTL = TASSEL_2 + MC_1 + TACLR; // SMCLK, upmode, clear TAR

}

void uart_Init(void)

{

P4SEL |= BIT4+BIT5; // P4.4,5 = USCI_A1 TXD/RXD

UCA1CTL1 |= UCSWRST; // **Put state machine in reset**

UCA1CTL1 |= UCSSEL_2; // SMCLK

UCA1BR0 = 9; // 1MHz 115200 (see User's Guide)

UCA1BR1 = 0; // 1MHz 115200

UCA1MCTL |= UCBRS_1 + UCBRF_0; // Modulation UCBRSx=1, UCBRFx=0

UCA1CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

UCA1IE |= UCRXIE; // Enable USCI_A1 RX interrupt

}

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

GPIO_Init();

I2C_Init();

timer0_Init();

uart_Init();

_EINT();

// __bis_SR_register(GIE);

PrintfBufLen = sprintf(PrintfBuf,"\r\nI2C Switch Debug:\r\n");

UARTwrite(PrintfBuf,PrintfBufLen);

while(1)

{

UartTx();

if(timeFlag == 1)

{

timeFlag = 0;

writeI2C();

}

}

}

// Timer0 A0 interrupt service routine

#pragma vector=TIMER0_A0_VECTOR

__interrupt void TIMER0_A0_ISR(void)

{

PJOUT ^= 0x01; // Toggle P1.0

timeFlag++;

}

#pragma vector=USCI_A1_VECTOR

__interrupt void USCI_A1_ISR(void)

{

// while (!(UCA1IFG&UCTXIFG)); // USCI_A1 TX buffer ready?

// UCA1TXBUF = UCA1RXBUF; // TX -> RXed character

}

#pragma vector = USCI_B1_VECTOR

__interrupt void USCI_B1_ISR(void)

{

switch(__even_in_range(UCB1IV,12))

{

case 0: break; // Vector 0: No interrupts

case 2: break; // Vector 2: ALIFG

case 4: break; // Vector 4: NACKIFG

case 6: break; // Vector 6: STTIFG

case 8: break; // Vector 8: STPIFG

case 10: break; // Vector 10: RXIFG

case 12: // Vector 12: TXIFG

if (TXByteCtr) // Check TX byte counter

{

UCB1TXBUF = *PTxData++; // Load TX buffer

TXByteCtr--; // Decrement TX byte counter

}

else

{

UCB1CTL1 |= UCTXSTP; // I2C stop condition

UCB1IFG &= ~UCTXIFG; // Clear USCI_B1 TX int flag

}

default: break;

}

}

Could you please help check this case? Thanks.

Best Regards,

Cherry