Hello,

What is the maximum possible clock frequency of UCxCLK input in SPI(eUSCI) slave mode with a certain SMCLK setting?

I can't find this infomrtion in both the datasheet and the user's guide.

Regards,

Oba

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

What is the maximum possible clock frequency of UCxCLK input in SPI(eUSCI) slave mode with a certain SMCLK setting?

I can't find this infomrtion in both the datasheet and the user's guide.

Regards,

Oba

Hey Oba,

I don't think it's well defined in terms of frequency, it's more define as the setup time for the master and slave devices on the bus.

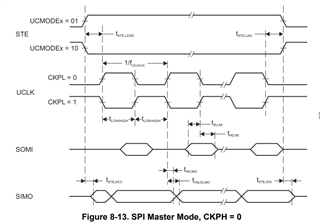

From this figure, you can see that f_UCxCLK is two of the T_LOW/HIGH time periods.

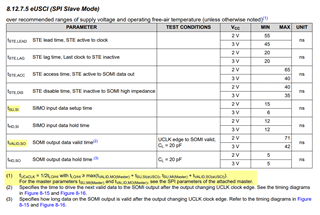

In Section 8.12.7.5 SPI Slave Table's notes, if specifies how to calculate F_UCxCLK

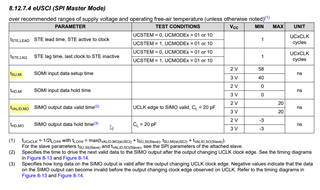

And for easier reference, here is the same table for SPI Master.

So with an MSP430FR2673 on each side, both powered at 3V, here is the calculation and we need to use the slowest one.

Master output - Slave input: T_valid,m0(master) + t_su,si (slave) = 20 ns + 6ns = 26ns

Slave out, master input: T_su,mi (master) + T_valid,s0(slave) = 42 ns + 40 ns = 82 ns

82ns * 2 = 164 ns.

1/164ns = ~ 6MHz

As shown, it does depend on the device on each side. So pull these numbers also from the Master device you are looking at to calculate if it'll be any faster or slower.

Thanks,

JD

Hello JD,

Thank you very much for your reply.

Doesn't it depend on SMCLK frequency?

I feel it is a little bit strange.

Actually, in my customer case, with 0.5MHz SMCLK configuration, it doesn't work with 1MHz SPI clock.

Regards,

Oba

Hello Oba,

I guess I misunderstood your question. I was addressing "what is the max possible SPI Slave speed?" but I guess you are basically asking "What is the slowest SMCLK can I have with a 1MHz SPI Clock?"

That one is not as clear to me. My understanding from the TRM is that in Slave/Target mode, the SPI bus clock is what actually clock in/out the data from the TX/RX shift registers. The SMCLK would only come into play with reading out and loading those registers or servicing interrupts.

There is not real way for the SPI target to clock stretch and tell the SPI Master it needs more time, so it will need to keep up with reading out the RX buffer and loading the TX buffer.

In terms of time, you will have 1 MHz / 8 bits, but you have to read out the received data and load the next data in that time, which will take some clocks to fetch and store, etc. Depending on the application code, would probably define the exact number of clocks needed, but as you mentioned, running at .5MHz (which is only 4 clock cycles per transaction) does not seem like enough.

I would estimate that at an absoluetly bare minimum, you need like 8-10 clocks to just read and load data, but if using interrupts, probably a multiple of that.

Hope this helps,

JD

Hello JD,

>I guess you are basically asking "What is the slowest SMCLK can I have with a 1MHz SPI Clock?"

Sorry, my explanation was not good. You are correct, it is what I wanted to ask.

They want to reduce the SMCLK frequency to realize lower power.

I understand that the shift register inside eUSCI works with SPI input clock and the problem is the speed between CPU and eUSCI buffer.

Let me check it with the customer.

Thanks for your support.

Regards,

Oba

**Attention** This is a public forum