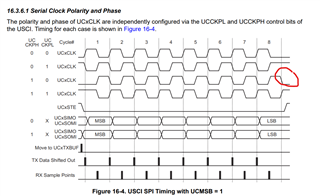

configuration:

UCB0CTL1 |= UCSWRST;

P1SEL |= SIMO + SOMI + CLK;

P1SEL2 |= SIMO + SOMI + CLK;

UCB0CTL0 = UCMST; //Master mode select

UCB0CTL0 |= UCSYNC; //syncron mode

UCB0CTL0 |= UCMSB; //MSB firs

UCB0CTL0 |= UCCKPH; //Clock Phase inactive state is low

//UCB0CTL0 |= UCCKPL; //The inactive state is high

UCB0CTL1 |= UCSSEL_3; //10b = SMCLK

UCB0BR0 = 16; //low byte

UCB0BR1 = 0; //high byte

IFG2 &= ~UCB0TXIFG;

IFG2 &= ~UCB0RXIFG;

UCB0CTL1 &= ~UCSWRST;

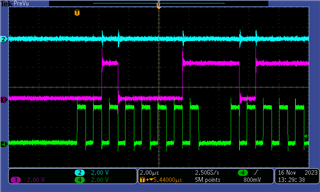

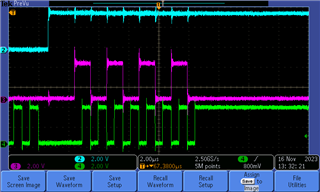

Green CLK

blue - Data/Code for nokia 5110 display

purple is data

tek00418.png is first byte

tek00425.png is last byte

Problem is not considering nokia 5110 clock for 8th bit if remain to high and not considering last 8bytes valid.

If i write again 8 bits the validation of previous 8bit will considering, but not current last 8bit .

transmitting: 1st Byte(not considering anything's on display); 2nd Byte(appear on 5110 1st data byte); 3st Byte(appear on 5110 2nd data byte)...

If I put Brake Point and reset Cip Select for CLK (Port1 Bit5), CLK is going to low and appear last Byte data on display.

Can you propose any solution?

Thanks