Hi,

Thank you for always teaching me!

Please tell me about the frequency settings.

When using SD24_B, the source frequency was set to SMCLK. However, when I looked at the User's Guide, I thought that the default setting was 1.048576 MHz.

"When crystal start-up is obtained and settled, the FLL stabilizes MCLK and SMCLK to 1.048576 MHz and fDCO = 2.097152 MHz."(5.2 UCS Operation)

I'm thinking of setting SMCLK, wondering if increasing the frequency will make a difference in AD conversion.

Initially, I thought that MCLK and SMCLK output the maximum frequency of 25MHz.

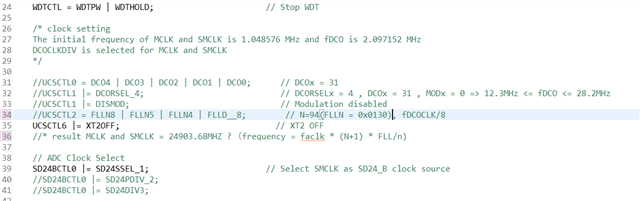

Therefore, I am currently creating a program using CCS12.5.0.

Attached is part of the program.

It just doesn't work. In the current program, I intended to set it to about 25MHz, but when I start it through debugging, it stops at the watchdog timer.

This seems to occur when setting DCO and DCORSEL at the same time.

Since it was stated that an appropriate range must be determined in order to generate a stable frequency, the values for DCORSEL, DCO, and MOD were determined. Since the desired frequency is approximately 25MHz, I intended to set DCORSELx = 4, DCOx = 31, MODx = 0, but it did not work.

(5.8.2 Clock Specifications, Table 5-5. DCO Frequency)

I think I'm using the wrong frequency setting program or setting the frequency range incorrectly, but I can't decide.

Could someone please enlighten me?

Thank you.

Toshiharu