Other Parts Discussed in Thread: MSP-GANG,

The MSP-GANG Cannot program MSP430F21x1 chips using the BSL. The communications between the PC and the MSP-GANG fail shortly after the FBSL or Fast-BSL has been loaded. I gave a very detailed account of this bug in an earlier post over 10 years ago! Still nothing has been done to fix it. I was recently bitten by this bug again and thought I would re-post.

This is NOT a corner case, TI's official programmer cannot program a single F21x1 chip that leaves the factory using the BSL.

My previous observations still stand and nothing has changed, so I won't reiterate all that, just refer the reader to my previous post.

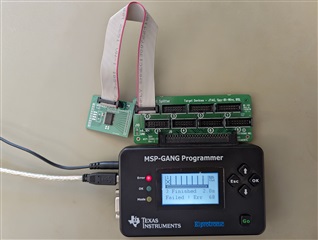

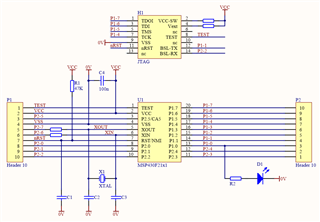

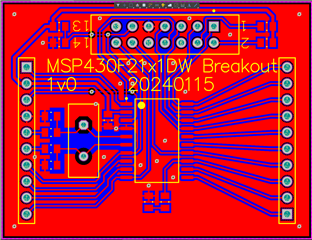

In an effort to illustrate this problem, and pre-empt the usual "you are doing it wrong" response, I have laid out a board with just the essential components. See the attached photo.

On the board is the MSP430, a 100nF Vcc bypass capacitor. a 47K pullup resistor and a 2.2nF capacitor to ground on the /RST pin, as specified in slau278ah, Figure 2-1.

I have assembled three such boards and loaded then variously with

MSP430F2121T Rev E

MSP430F2131T Rev I

MSP430F2131 Rev K

All three boards present the same problem. These are all the chip revisions I had on hand. I have no reason to doubt all earlier and later silicon revisions would behave the same.

The JTAG works fine and can read out the memory of the (Blank) chips.

The BSL fails with error 68 shortly after loading the FBSL.

I don't know what else I can do to convince TI / Elprotonoic that this is a real problem and not just user error.

PLEASE FIX THIS BUG!!!!!

PLEASE FIX THIS BUG!!!!!

PLEASE FIX THIS BUG!!!!!

Regards,

Sean Gallagher.

log..

Openning target..Done

.............

4 : init target

5 : Loading FBSL

6 :

ERROR 68: FBSL initialization error

ERROR 68: FBSL initialization error

ERROR 68: FBSL initialization error

Closing target.. 0 : Finished

ERROR 68: FBSL initialization error