As with my present source code, the SVSLPE bits is clear.

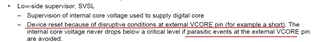

(SVS low-side power-on reset is disabled)

PMMRIE = SVSHPE;

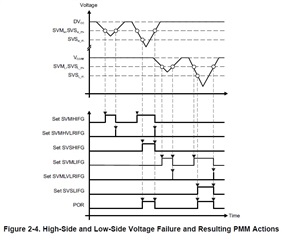

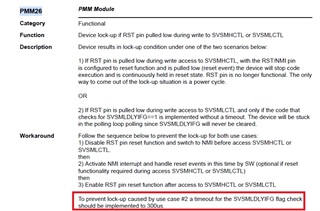

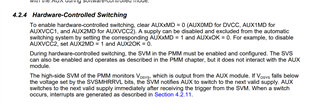

What happens if Vcore drop but there is no POR? (e.g. the MCU will stuck in reset state)

How to simulate Vcore drop but DVCC is kept (as Figure 2-4 in the user guide)?