Tool/software:

I tested the current consumption when setting the MCU in LPM3 mode.

Configuration #1: unused pins to inputs and disable internal pull-up resistors (P4.1 to P4.6)

result: current consumption is 8 uA

Configuration #2: Set unused pins to low outputs (P4.1 to P4.6)

result: current consumption is 200 uA

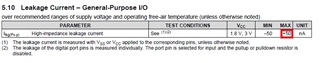

Why is the leakage current I/O so high (expected 0.3 uA)?