Tool/software:

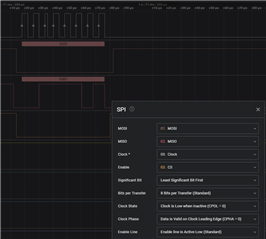

I am using the SPI of my MSP430F5503 as a slave on the UCB1 interface with the following configuration.

UCB1IFG &= ~UCRXIFG;

UCB1CTL1 = UCSWRST; // Enable SW reset - Starts config mode

UCB1CTL0 = UCSYNC + UCCKPH + UCMODE_2;

UCB1RXBUF = 0x00;

UCB1TXBUF = 0x00;

UCB1CTL1 &= ~UCSWRST; // **Initialize USCI state machine** - restart usci with new settings

_NOP();

UCB1IE |= UCRXIE ; // UCB1 RX & TX Interrupt enable

At the beginning of the program start, the SPI works, and both sending and receiving function without any issues. It does what it is supposed to. The USCI40 error from the Errata Sheet also does not occur, and sending as a slave is not affected.

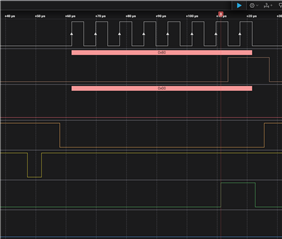

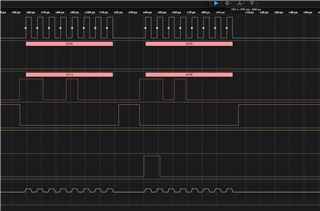

After an indefinite period, sometimes 2 hours, sometimes 1 day, the microcontroller stops receiving data correctly over SPI. I have checked this with the logic analyzer, see below:

However, instead of receiving 0xBC, the microcontroller receives 0x78—binary, instead of 0b1011 1100, it gets 0b0111 1000. You can see that the byte is suddenly shifted one bit to the left. Resetting the SPI doesn't help; only a restart of the msp430 fixes the problem.

Transmitting over SPI, i.e., TX, still works.

Below I have included the code of my SPI interrupt again. Maybe I am already making a major mistake here.

#pragma vector=USCI_B1_VECTOR

__interrupt void USCI_B1_interrupt(void)

{

switch(__even_in_range(UCB1IV,4))

{

case 0: break; // Vector 0 - no interrupt

case 2:

//////////////////////////

//// SPI RX Interrupt ////

//////////////////////////

// LPM0_EXIT;

if(knx_txstate != KNX_TXSTATE_IDLE && knx_txstate != KNX_TXSTATE_WAIT)

{

__delay_cycles(200 cyclesPerUs);

ncn51_tx_nextbyte(true);

}

else

{

UCB1TXBUF = 0x00;

}

// Byte received, read and clear flag

char rxbyte;

rxbyte = UCB1RXBUF;

if(rxbyte == 0xBC){

knx_txstate = KNX_TXSTATE_WAIT;

}

LED2_ON;

// store into ringbuffer

if(ringbufferIsFull(&spi_rx_buf) || (utilNormalizeOverflowDiffInt(TA0R, lastReceive) < 1000 ticksPerUs) && knx_txstate != KNX_TXSTATE_IDLE){

_NOP()

}

else{

lastReceive=TA0R;

ringbufferPushElement(&spi_rx_buf,(unsigned char *) &rxbyte);

}

break;

case 4:

//////////////////////////

//// SPI TX Interrupt ////

//////////////////////////

default: break;

}

}

I've run out of ideas. Maybe someone has ideas or can give me tips on what I can try. If more information is needed, I will, of course, provide it as quickly as possible.

On the left, the image during the occurrence of the error, and on the right, the image when the MSP430 is receiving everything correctly.

On the left, the image during the occurrence of the error, and on the right, the image when the MSP430 is receiving everything correctly.